# ICs for Data Communications

# DATA HANDBOOK

**Philips Semiconductors**

**PHILIPS**

#### **QUALITY ASSURED**

Our quality system focuses on the continuing high quality of our components and the best possible service for our customers. We have a three-sided quality strategy: we apply a system of total quality control and assurance; we operate customer-oriented dynamic improvement programmes; and we promote a partnering relationship with our customers and suppliers.

#### PRODUCT SAFETY

In striving for state-of-the-art perfection, we continuously improve components and processes with respect to environmental demands. Our components offer no hazard to the environment in normal use when operated or stored within the limits specified in the data sheet.

Some components unavoidably contain substances that, if exposed by accident or misuse, are potentially hazardous to health. Users of these components are informed of the danger by warning notices in the data sheets supporting the components. Where necessary the warning notices also indicate safety precautions to be taken and disposal instructions to be followed. Obviously users of these components, in general the set-making industry, assume responsibility towards the consumer with respect to safety matters and environmental demands.

All used or obsolete components should be disposed of according to the regulations applying at the disposal location. Depending on the location, electronic components are considered to be 'chemical', 'special' or sometimes 'industrial' waste. Disposal as domestic waste is usually not permitted.

# ICs for Data Communications

## **CONTENTS**

|            |                                                                | page |

|------------|----------------------------------------------------------------|------|

| SECTION 1  | GENERAL INFORMATION                                            | 5    |

| SECTION 2  | DIGITAL DATA COMMUNICATIONS                                    | 57   |

| SECTION 3  | CDUSCC USER'S GUIDE                                            | 513  |

| SECTION 4  | DUSCC USER'S GUIDE                                             | 617  |

| SECTION 5  | LINEAR DATA COMMUNICATIONS                                     | 667  |

| SECTION 6  | FIBRE OPTIC PRODUCTS                                           | 795  |

| SECTION 7  | FUTUREBUS+ PRODUCTS                                            | 915  |

| SECTION 8  | PACKAGE OUTLINES                                               | 969  |

| SECTION 9  | NORTH AMERICAN SALES OFFICES, REPRESENTATIVES AND DISTRIBUTORS | 997  |

| APPENDIX A | DATA HANDBOOK SYSTEM                                           | 1000 |

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and North American Philips Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.

Philips Semiconductors and Philips Electronics North America Corporation registers eligible circuits under the Semiconductor Chip Protection Act

© Copyright Philips Electronics North America Corporation 1994

#### **Philips Semiconductors**

## **Preface**

**ICs for Data Communications**

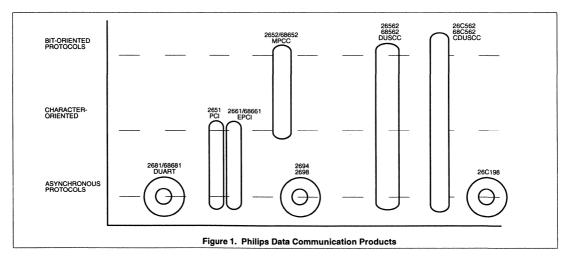

Data Communications is one of the fastest growing markets in electronics and one in which Philips Semiconductors has had a leadership position for many years. Our industry standard UARTs are complemented with the advanced architecture of the Dual Universal Serial Communications Controller (DUSCC) products and, more recently, by the innovative I/O Processor family. Taking advantage of an advanced CMOS technology, this entire product line represents the most comprehensive in the industry and it continues to grow.

In addition to the product focus, Philips Semiconductors continues its committment to the highest levels of quality to insure our customers of cost effective ownership and world class reliability. In addition to the Digital Data Communication product family, Philips Semiconductors offers a very extensive portfolio of semiconductor products, the details of which can be obtained from your local sales office.

#### **Philips Semiconductors**

# Section 1 General information

#### **ICs for Data Communications**

#### CONTENTS

| Functional Index                                            | 7  |

|-------------------------------------------------------------|----|

| Alphanumeric Product List                                   | g  |

| Product Status                                              | 10 |

| Ordering information                                        | 11 |

| Network terms                                               | 12 |

| Networking acronyms                                         | 18 |

| Understand datacom protocols by examining their structures  | 35 |

| A designer's review of data communications                  | 40 |

| Complex datacom peripheral ICs interface to many processors | 48 |

| Controller contends with multiple protocols                 | 49 |

# **Functional Index**

#### **ICs for Data Communications**

#### **CONTENTS**

| Preface               |                                                                                    | 3   |

|-----------------------|------------------------------------------------------------------------------------|-----|

| Section 1 Gen         | eral Information                                                                   | 5   |

| Alphanumeric F        | Product List                                                                       | 9   |

| Product Status        |                                                                                    | 10  |

| Ordering Inform       | nation                                                                             | 11  |

|                       |                                                                                    |     |

| Section 2 Digit       | tal Data Communications Data Sheets                                                | 57  |

|                       | Asynchronous Communication Product Line (UARTs)                                    | 58  |

|                       | Synchronous Communications Product Line                                            | 59  |

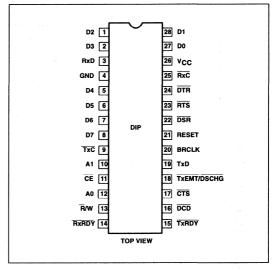

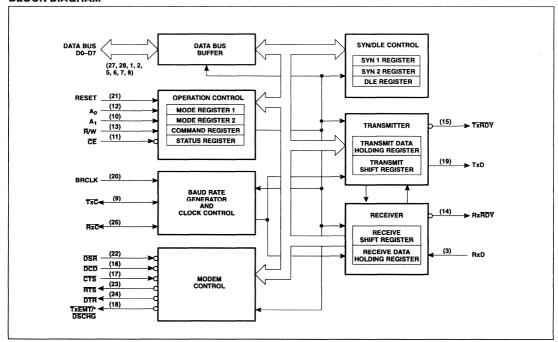

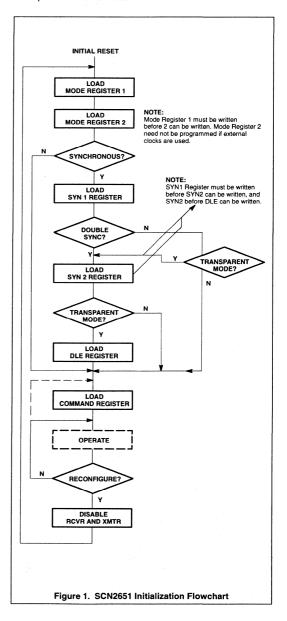

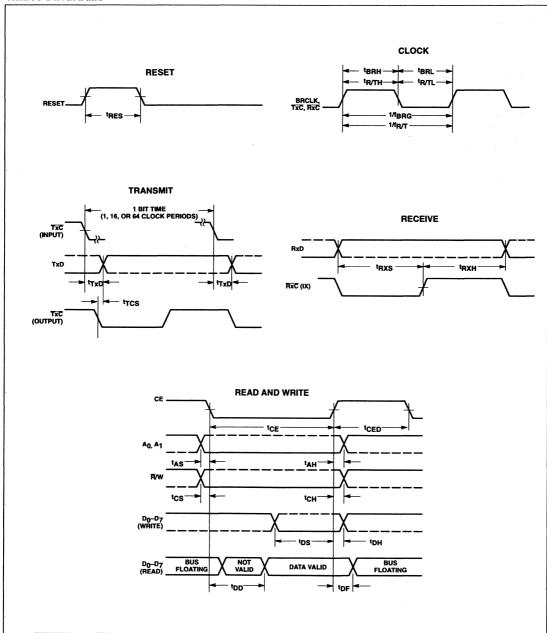

| SCN2651               | Programmable communications interface (PCI)                                        | 60  |

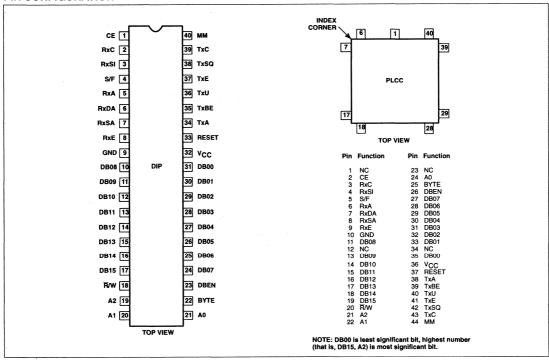

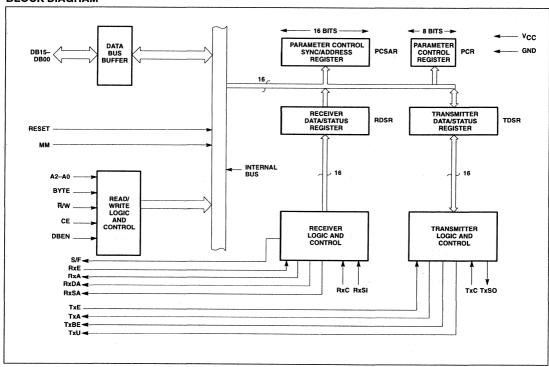

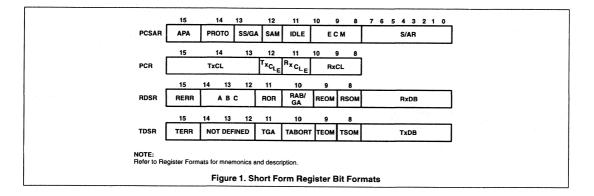

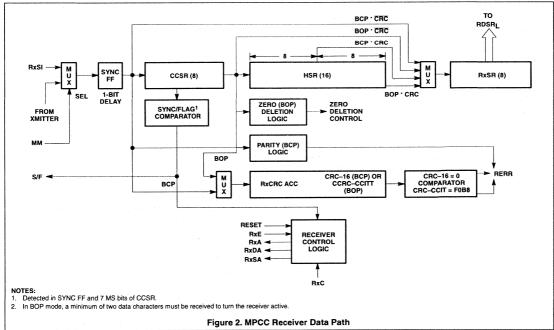

| SCN2652/SCN           | 68652 Multi-protocol communications controller (MPCC)                              | 75  |

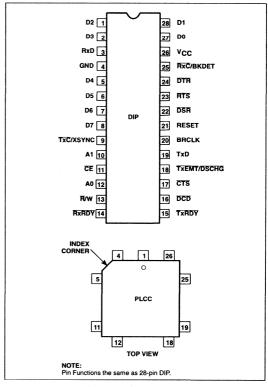

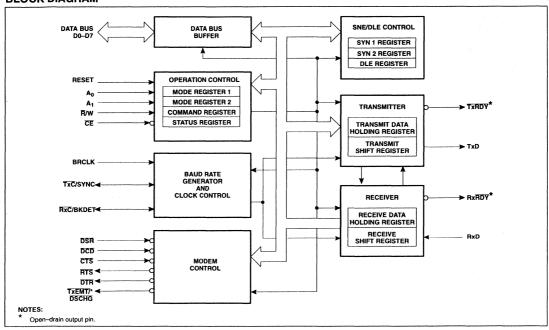

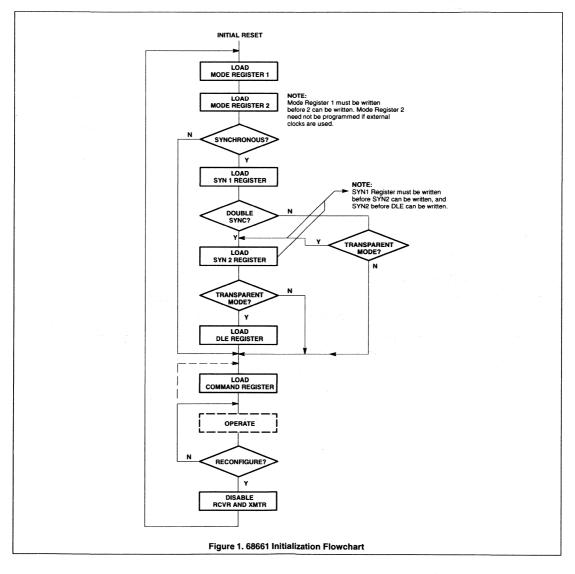

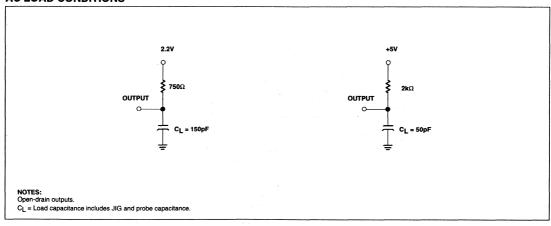

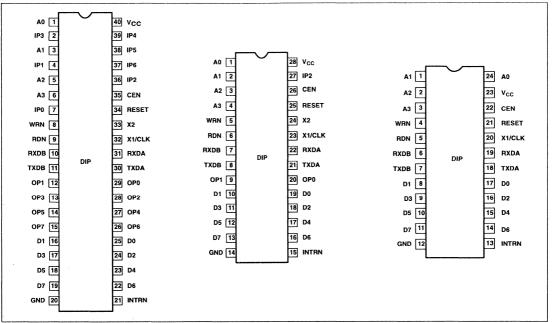

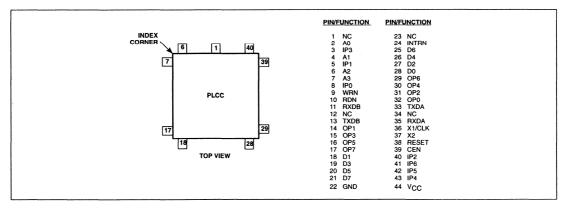

| SCN2661/SCN           | 68661 Enhanced programmable communications interface (EPCI)                        | 97  |

| SCN2681               | Dual asynchronous receiver/transmitter (DUART)                                     | 116 |

| AN405                 | SCN2681/SCN68681 and SCC2691 data communications                                   | 138 |

| SCN2681T              | Dual asynchronous receiver/transmitter (DUART)                                     | 143 |

| SCN68681              | Dual asynchronous receiver/transmitter (DUART)                                     | 154 |

| SCC2691               | Universal asynchronous receiver/transmitter (UART)                                 | 176 |

| SCC2692               | Dual asynchronous receiver/transmitter (DUART)                                     | 195 |

| AN414                 | SCC2692 differences from the SCN2681                                               | 218 |

|                       | Extended baud rates for SCN2681, SCN68681, SCC2691, SCC2692, SCC68681 and SCC2698B | 220 |

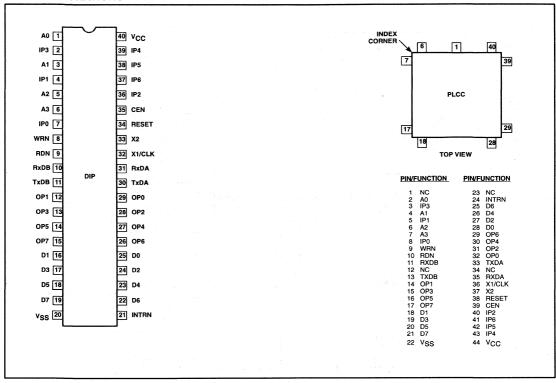

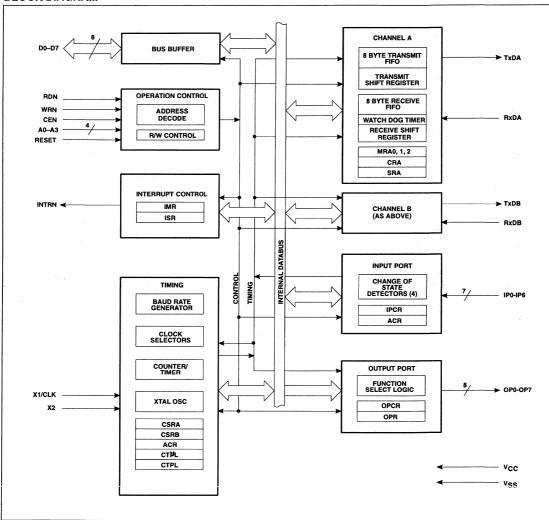

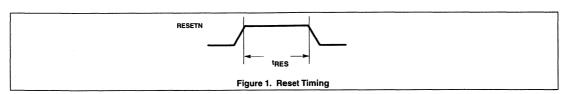

| SCC68692              | Dual asynchronous receiver/transmitter (DUART)                                     | 222 |

| AN415                 | SCC68692 differences from the SCN68681                                             | 246 |

| SC26C92               | Dual universal asynchronous receiver/transmitter (DUART)                           | 248 |

| SC26C94               | Quad universal asynchronous receiver/transmitter (QUART)                           | 271 |

| SC68C94               | Quad universal asynchronous receiver/transmitter (QUART)                           | 302 |

|                       | SC26C94 and SC68C94 (QUARTs) interrupt system and processor interface              | 333 |

| SCC2698B              | Enhanced octal universal asynchronous receiver/transmitter (Octal UART)            | 336 |

| AN410B                | SCC2698B Octal universal asynchronous receiver/transmitter (Octal-UART)            | 359 |

| SC26C198              | Octal universal asynchronous receiver/transmitter (UART)                           | 371 |

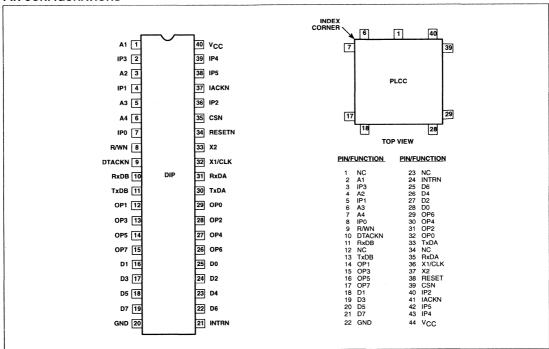

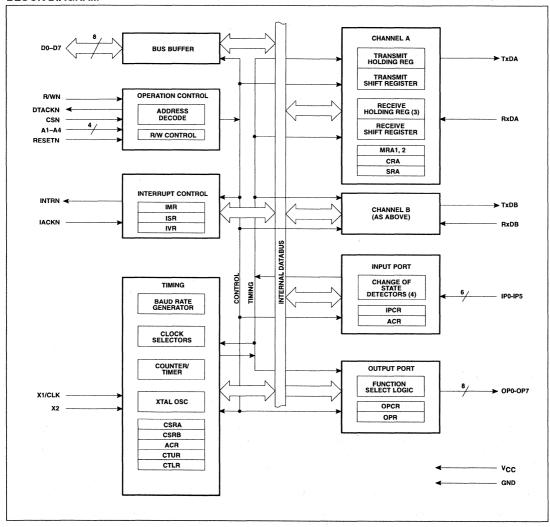

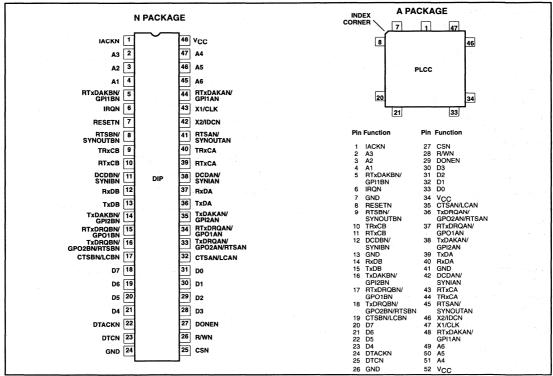

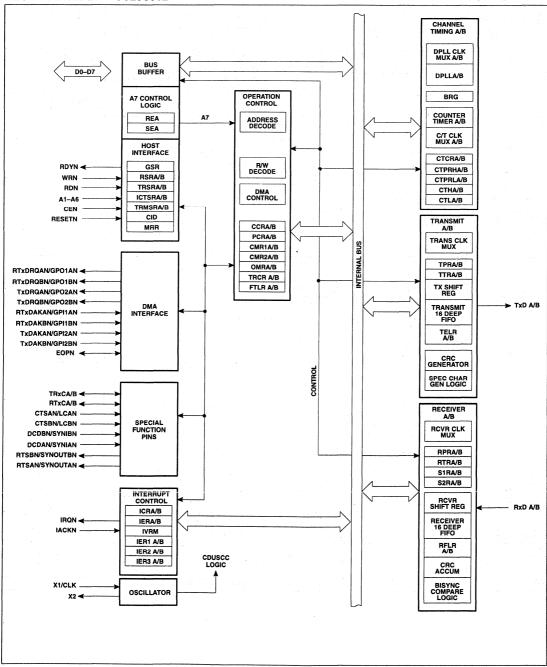

| SCN26562              | Dual universal serial communications controller (DUSCC)                            | 413 |

| SCN68562              | Dual universal serial communications controller (DUSCC)                            | 430 |

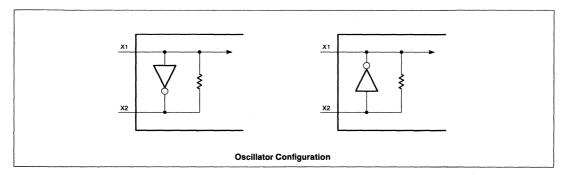

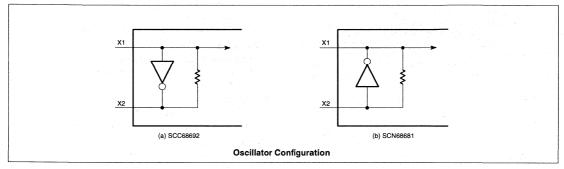

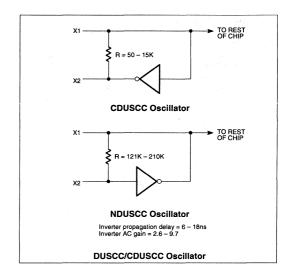

| AN413                 | Using the datacomm product's on-chip oscillator                                    | 444 |

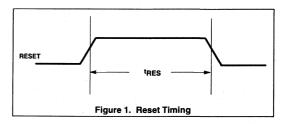

| AN419                 | DUSCC initialization procedures                                                    | 446 |

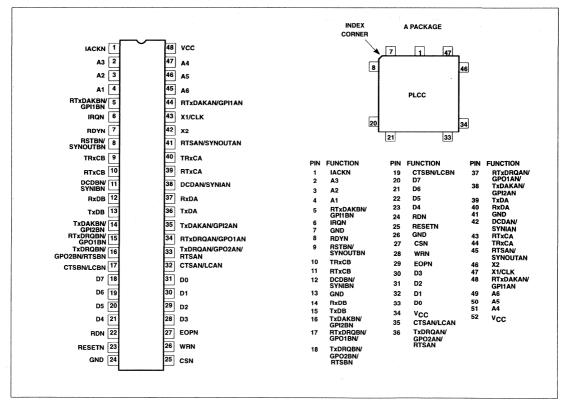

| SC26C562              | CMOS dual universal serial communications controller (CDUSCC)                      | 456 |

| SC68C562              | CMOS Dual universal serial communications controller (CDUSCC)                      | 474 |

| AN416                 | User notes for the SCN68/26562 (NDUSCC) and SC68/26C562 (CDUSCC)                   | 495 |

| Section 3 CDU         | SCC User's Guide                                                                   | 513 |

| Table of Conten       | ts                                                                                 | 514 |

|                       |                                                                                    | 514 |

| Section 4 DUS         | CC User's Guide                                                                    | 617 |

| Table of Conten       | ts                                                                                 | 618 |

|                       |                                                                                    | 618 |

| Section 5 Linea       | ar Data Communications Data Sheets                                                 | 667 |

| MC145406              | EIA-232-D/V.28 driver/receiver                                                     | 669 |

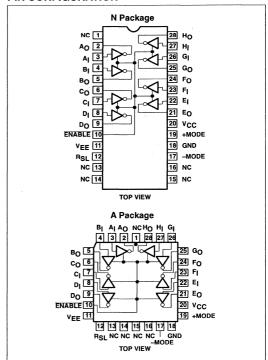

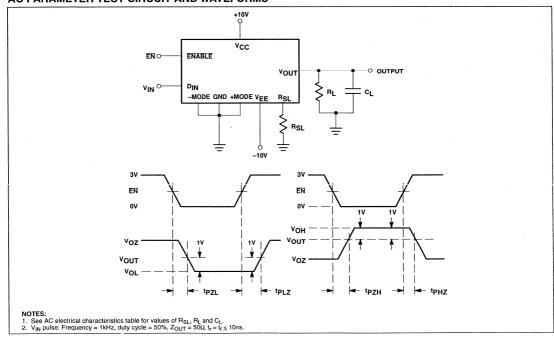

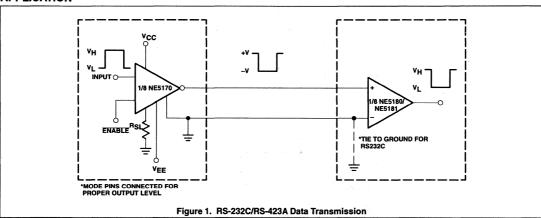

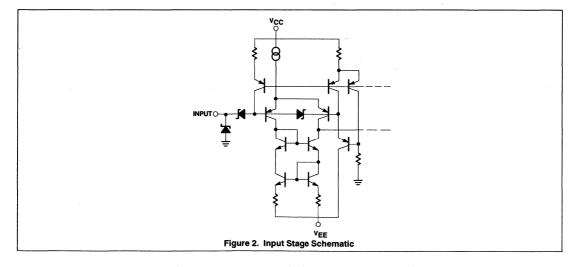

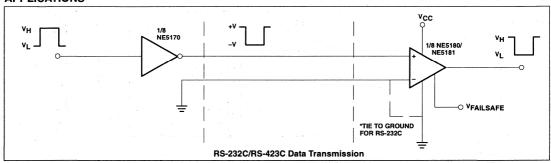

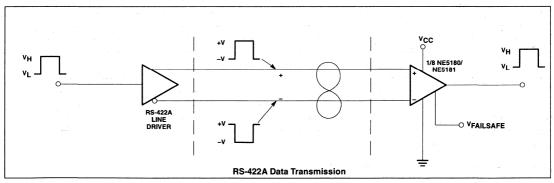

| NE5170                | Octal line driver                                                                  | 674 |

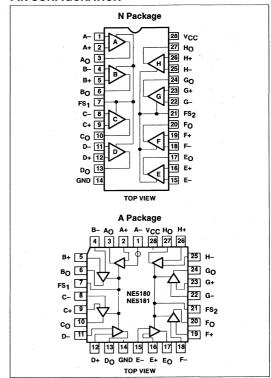

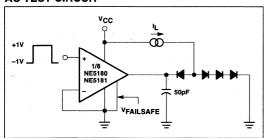

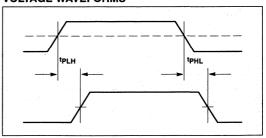

| NE5180/NE518          | 1 Octal differential line receiver                                                 | 680 |

| AM26LS31              | Quad high-speed differential line driver                                           | 685 |

| AM26LS32/             |                                                                                    |     |

| AM26LS33<br>AM26LS32B |                                                                                    | 690 |

| AIVIZOL S32B          | Quad high-speed differential line receivers                                        | 693 |

7

June 1994

# ICs for Data Communications

# **Functional Index**

| NE5050             | Power line modem                                                               | 696  |

|--------------------|--------------------------------------------------------------------------------|------|

| NE5080             | High-speed FSK modern transmitter                                              | 702  |

| NE5081             | High-speed FSK modem receiver                                                  | 707  |

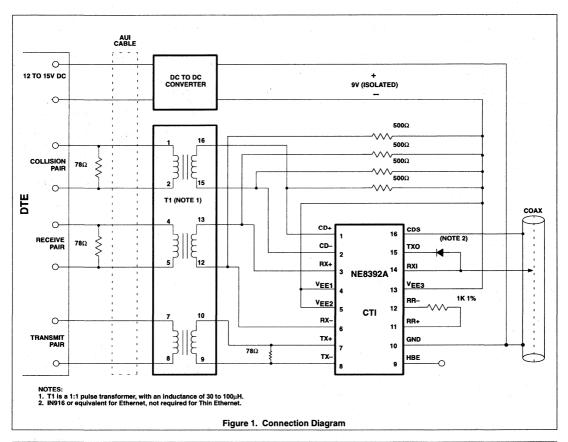

| NE8392A            | Coaxial transceiver interface for Ethernet/Thin Ethernet                       | 710  |

| NE8392C            | Coaxial transceiver interface for Ethernet/Thin Ethernet                       | 719  |

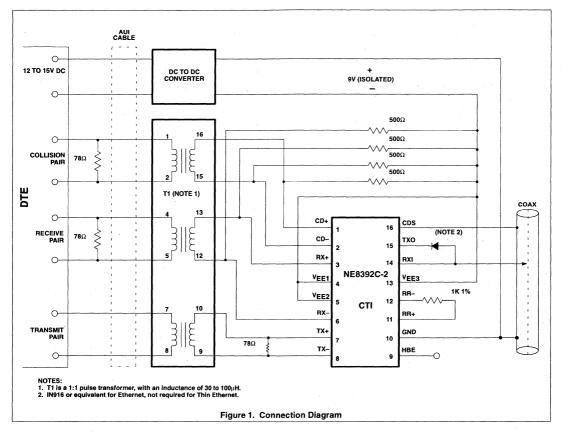

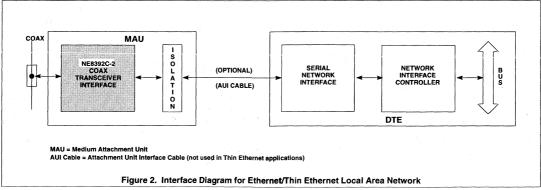

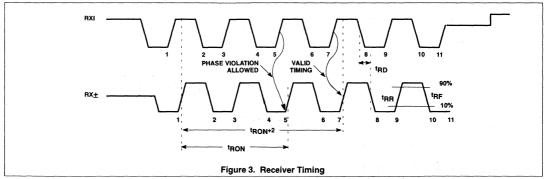

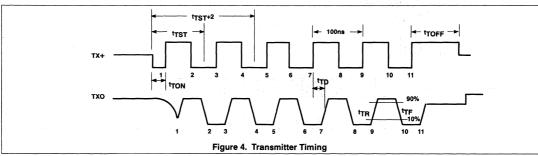

| NE8392C-2          | Coaxial transceiver interface for Ethernet/Thin Ethernet                       | 728  |

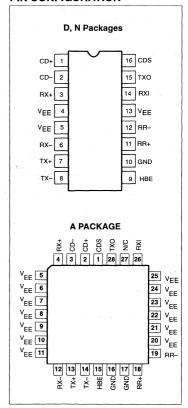

| NE86C92            | Twisted-pair transceiver interface                                             | 737  |

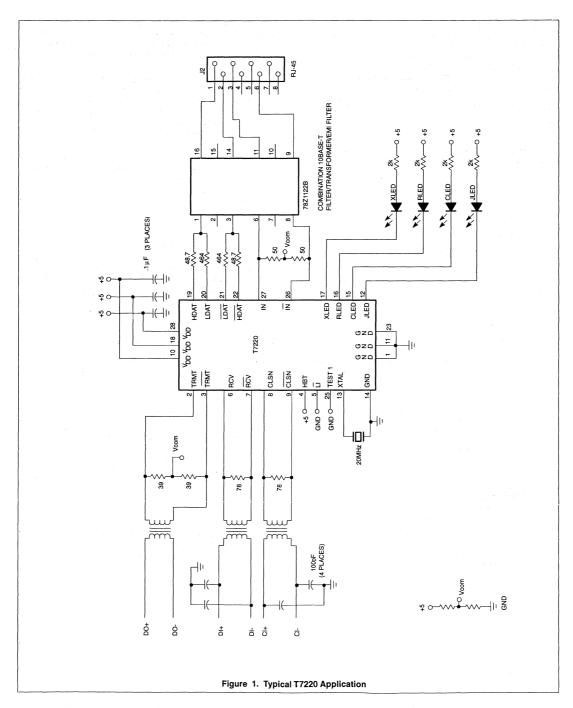

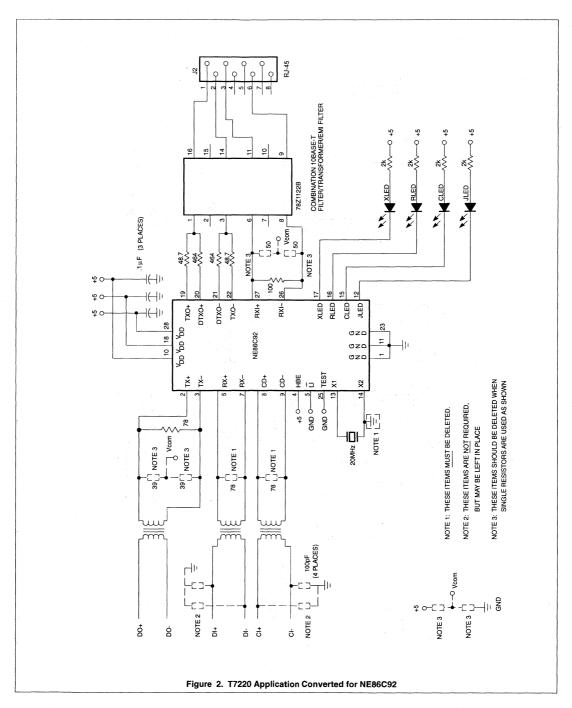

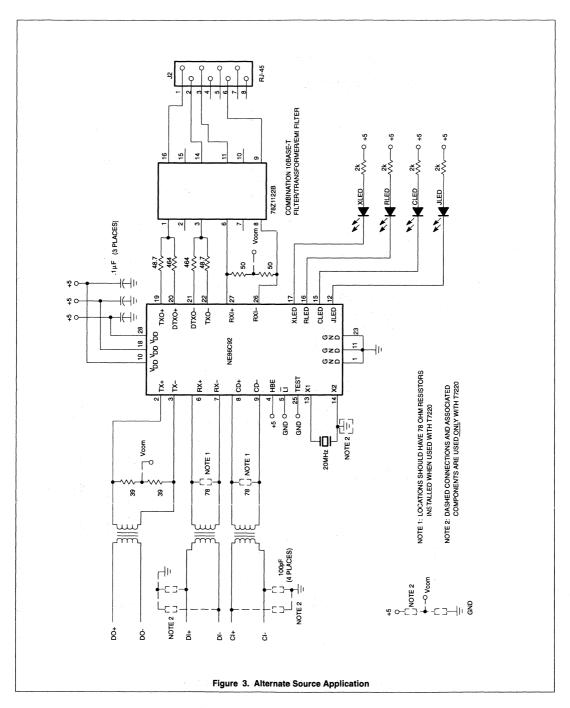

| AN4001             | Using the NE86C92 10BASE-T transceiver in AT&T T7220 applications              | 749  |

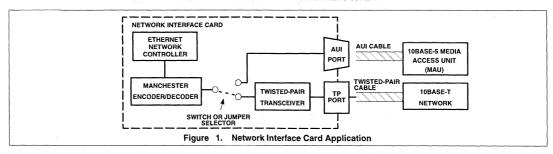

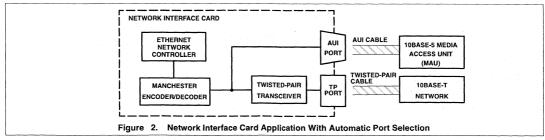

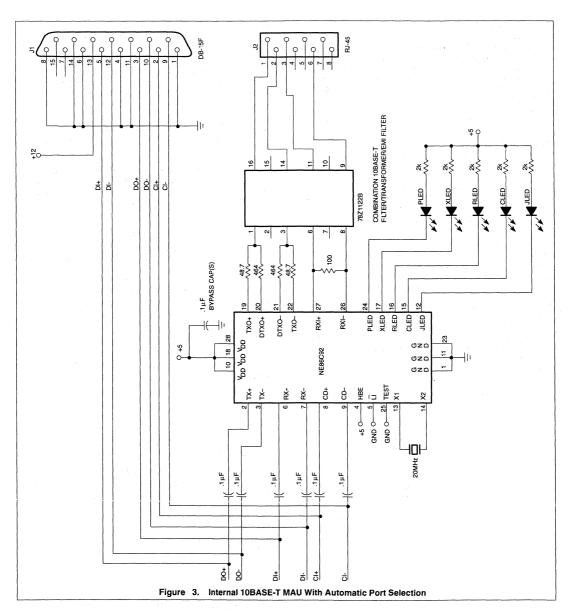

| AN4002             | Automatic selection between AUI port and internal NE86C92 10BASE-T transceiver | 753  |

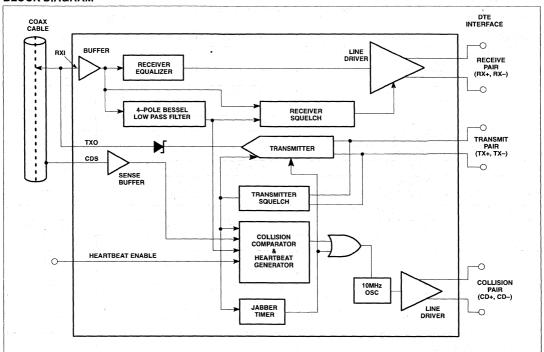

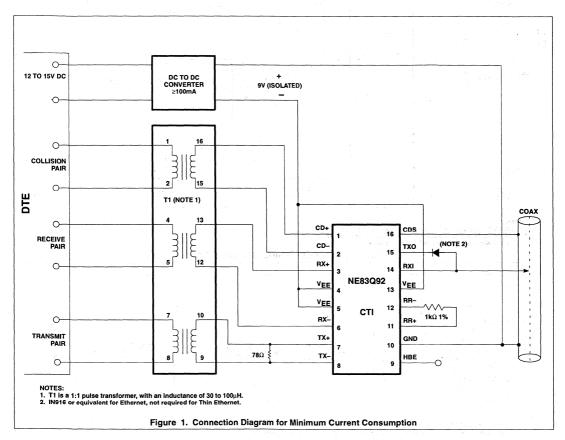

| NE83Q92            | Low-power coaxial Ethernet transceiver                                         | 755  |

| NE83Q93            | Enhanced coaxial Ethernet transceiver                                          | 765  |

| NE83C92            | Low-power coaxial Ethernet transceiver                                         | 776  |

| NE83Q94            | Miniature coaxial Ethernet transceiver                                         | 785  |

| Section 6 Fibre 0  | Optic Products Data Sheets                                                     | 795  |

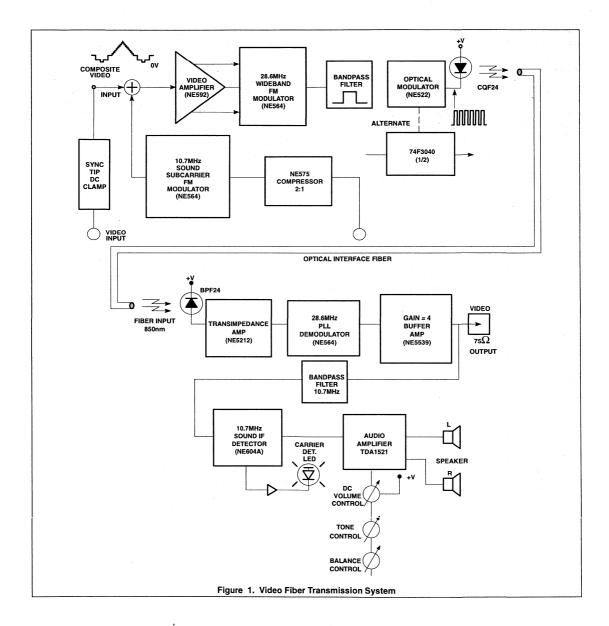

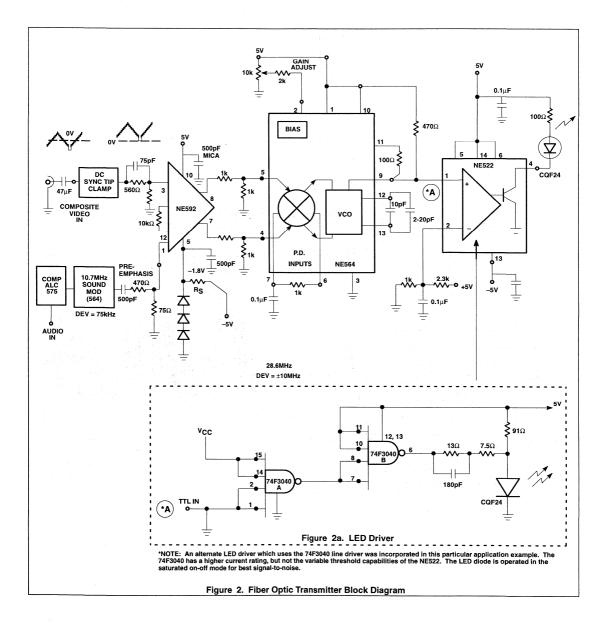

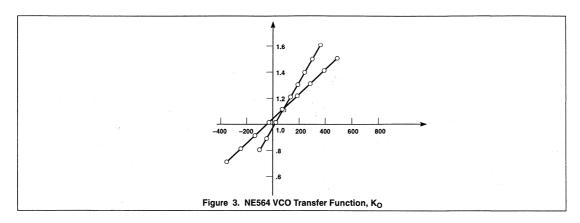

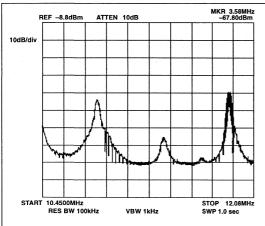

| AN1434             | A phase locked fiber optic system using FM modulation                          | 797  |

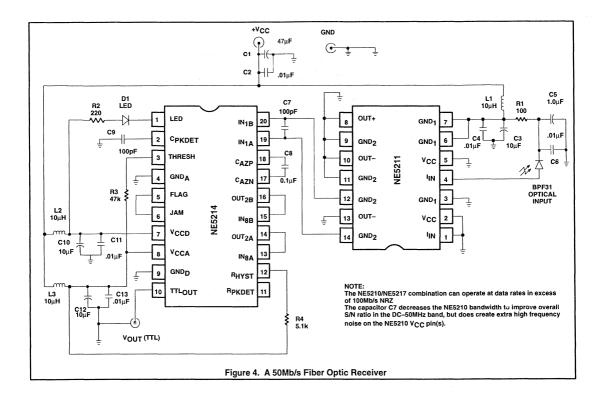

| AN1443             | Low cost, TTL fiber optic receivers for up to 100Mb/s NRZ                      | 808  |

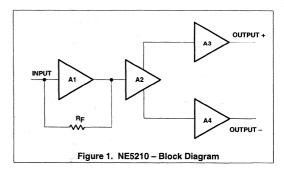

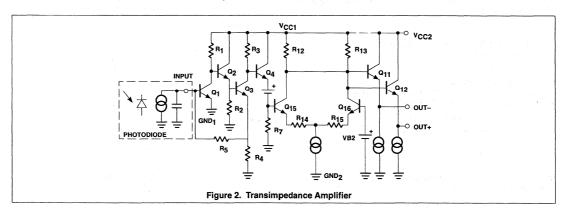

| NE5210             | Transimpedance amplifier (280MHz)                                              | 819  |

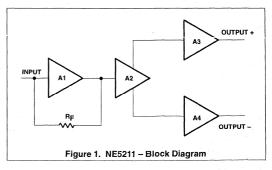

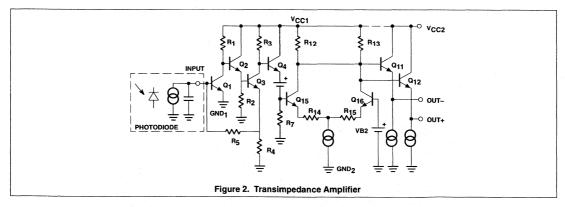

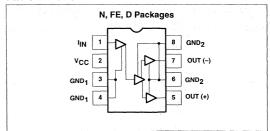

| NE/SA5211          | Transimpedance amplifier (180MHz)                                              | 832  |

| NE/SA/SE5212A      | Transimpedance amplifier (140MHz)                                              | 847  |

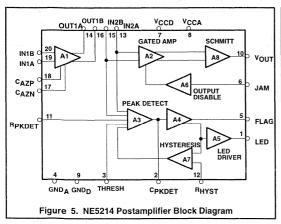

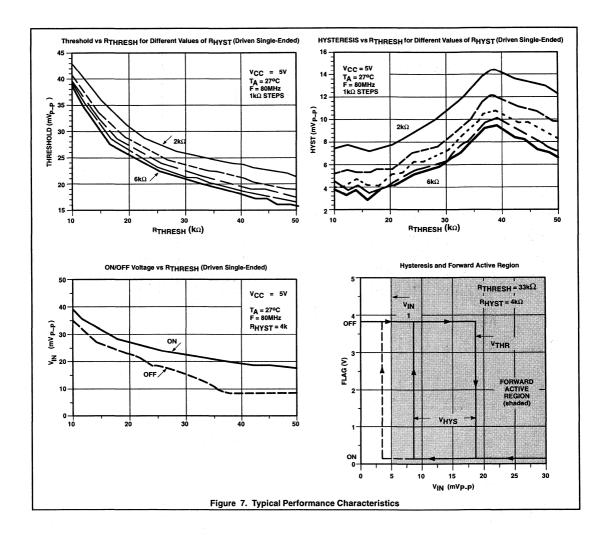

| NE/SA5214          | Postamplifier with link status indicator                                       | 861  |

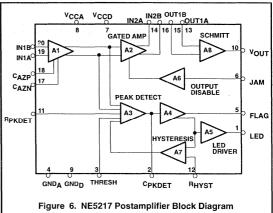

| NE/SA5217          | Postamplifier with link status indicator                                       | 867  |

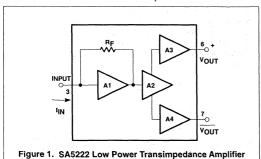

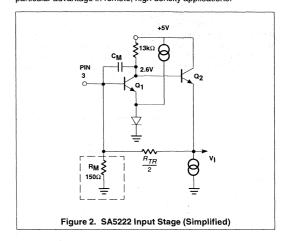

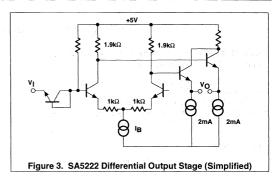

| SA5222             | Low-power FDDI transimpedance amplifier                                        | 874  |

| AN4003             | Fiber optic receiver applications note                                         | 881  |

| SA5223             | Wide-dynamic-range AGC                                                         | 893  |

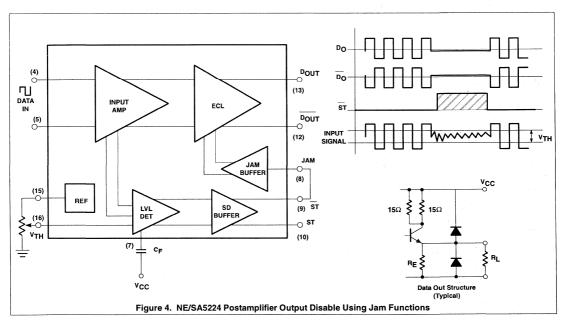

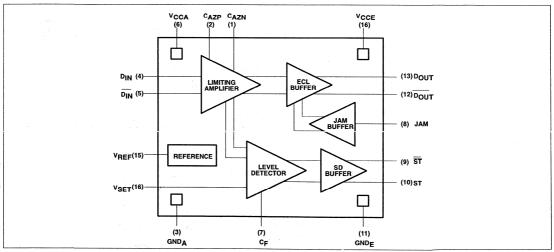

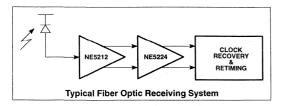

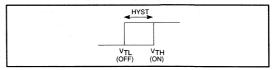

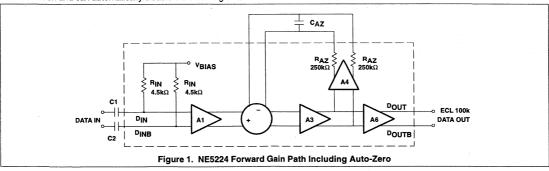

| NE/SA5224          | FDDI fiber optic postamplifier                                                 | 896  |

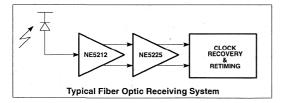

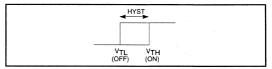

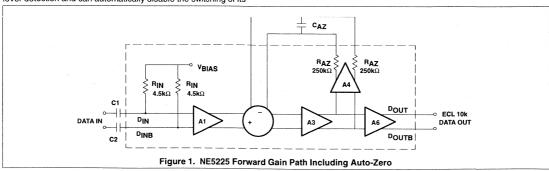

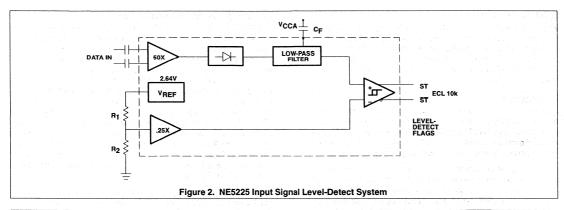

| NE/SA5225          | Fiber optic postamplifier                                                      | 901  |

| AN1435             | A family of wideband low noise transimpedance amplifiers                       | 906  |

| Section 7 Future   | ebus+ Products                                                                 | 915  |

|                    | Introduction: Futurebus+ / BTL: A high performance standard                    |      |

|                    | for advanced computing and communication systems                               | 917  |

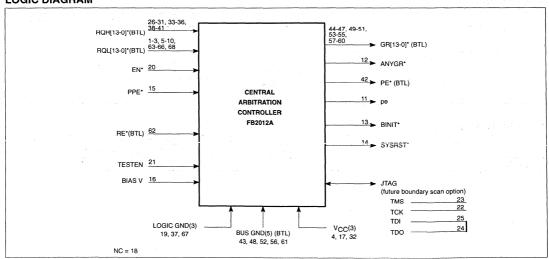

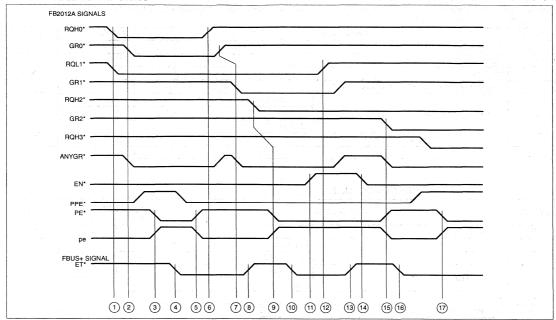

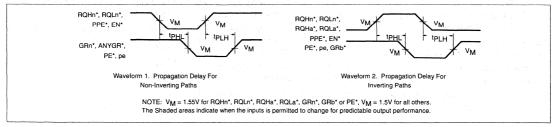

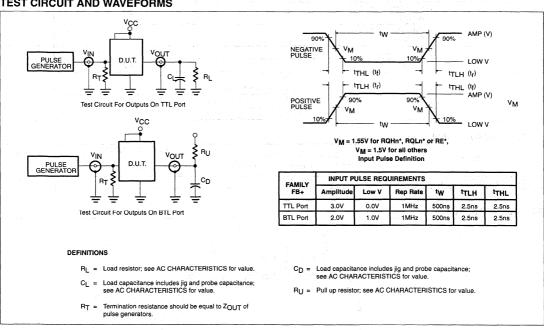

| FB2012A            | Futurebus+ central arbitration controller                                      | 919  |

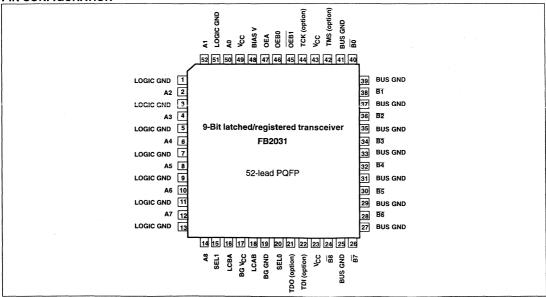

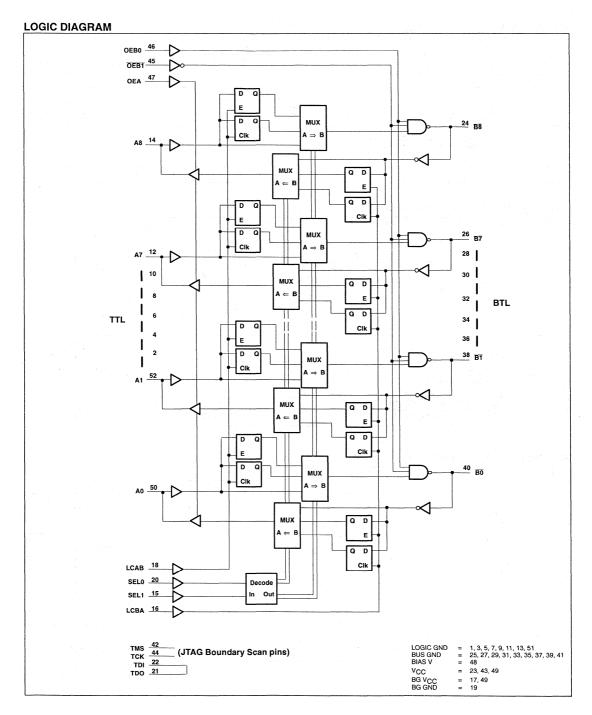

| FB2031             | 9-bit latched/registered/pass-thru Futurebus+ transceiver                      | 928  |

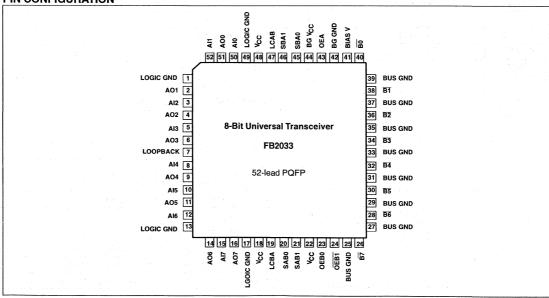

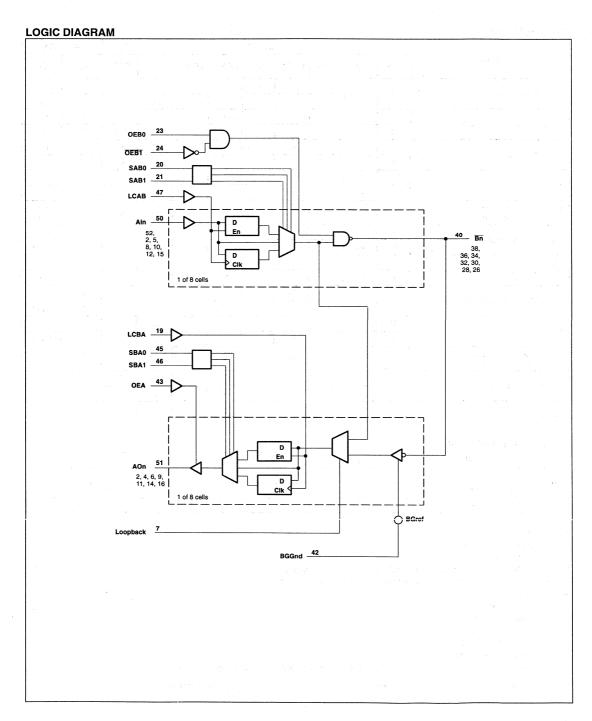

| FB2033             | 8-bit latched/registered/pass-thru Futurebus+ universal interface transceiver  | 941  |

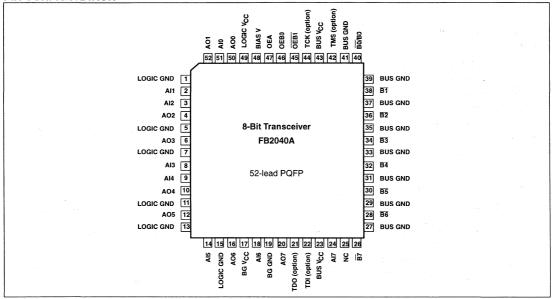

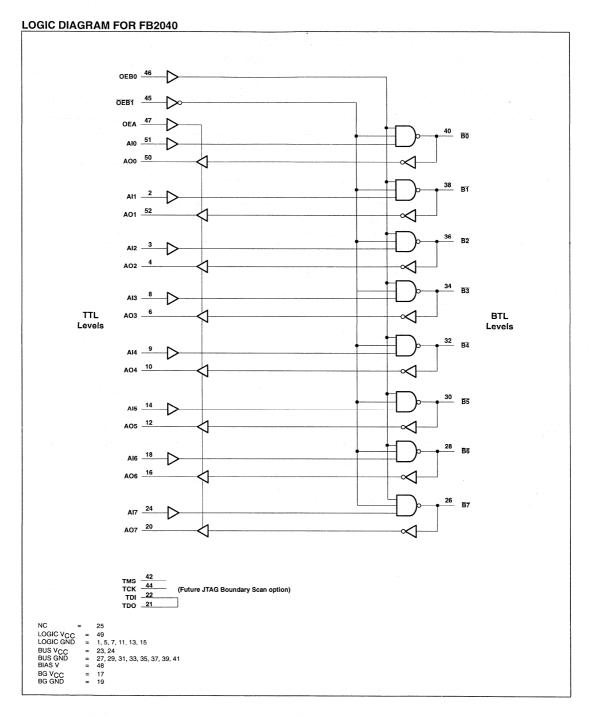

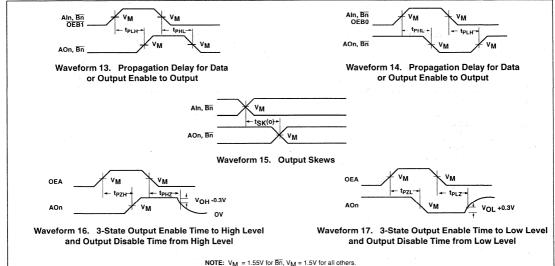

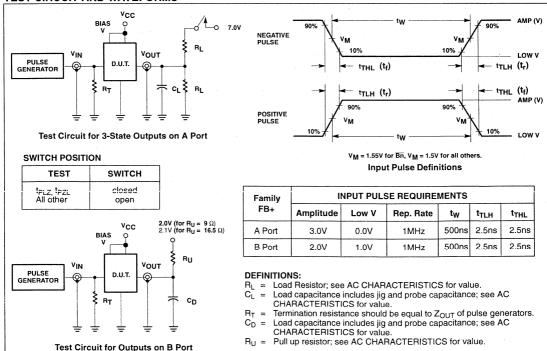

| FB2040A            | 8-bit Futurebus+ transceiver                                                   | 951  |

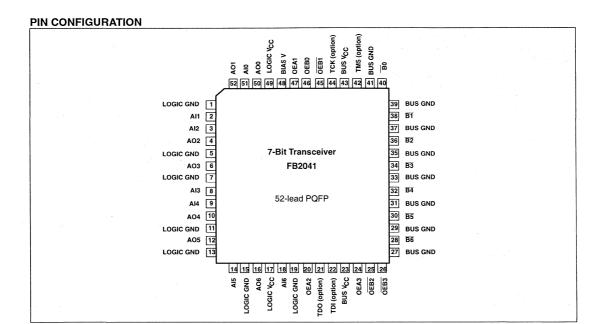

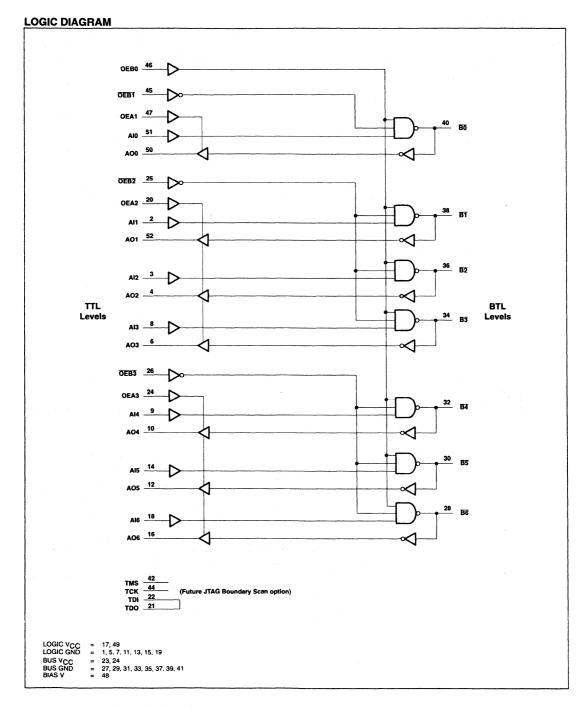

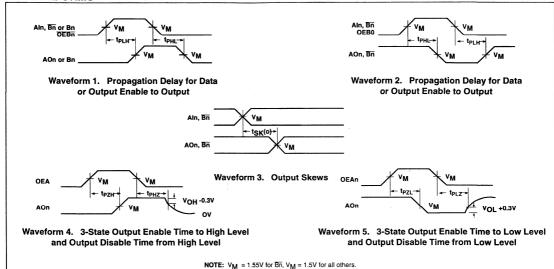

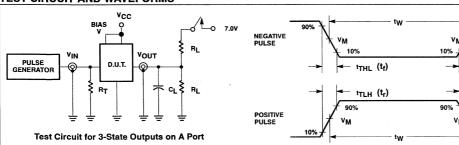

| FB2041             | 7-bit Futurebus+ transceiver                                                   | 959  |

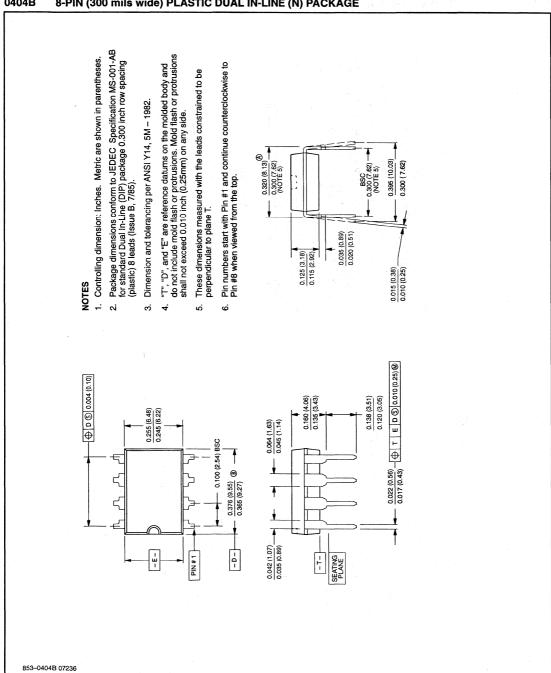

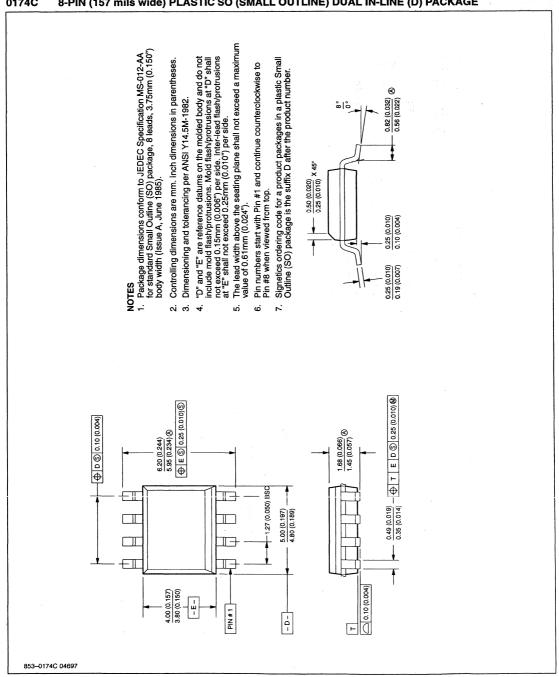

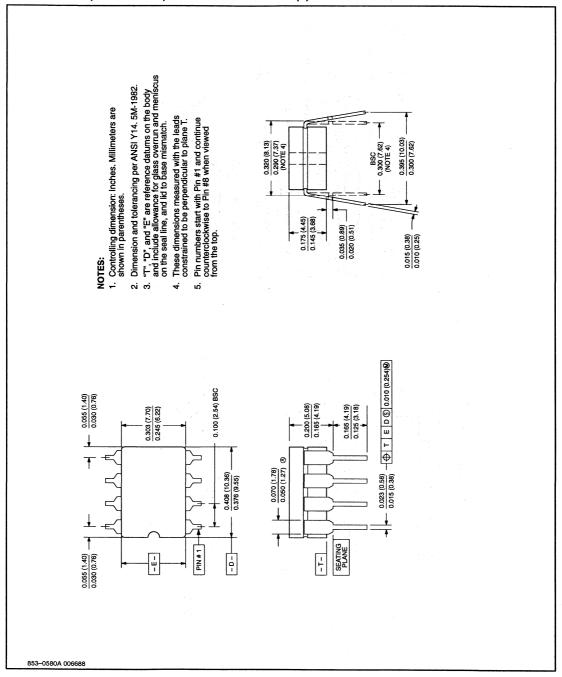

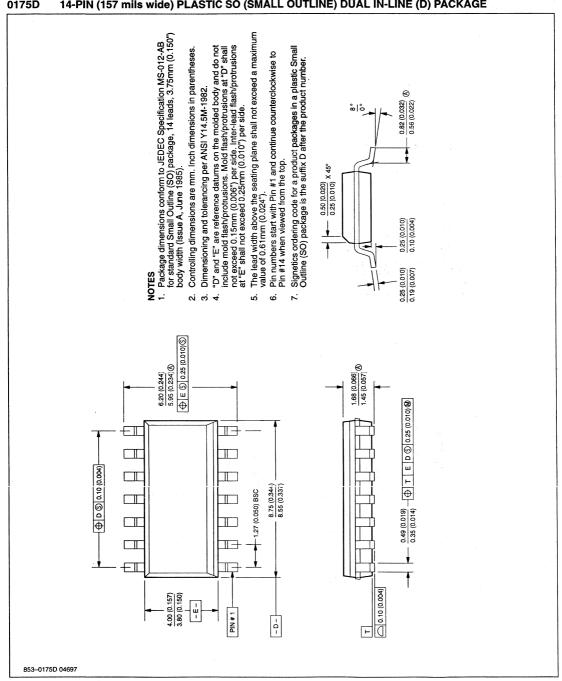

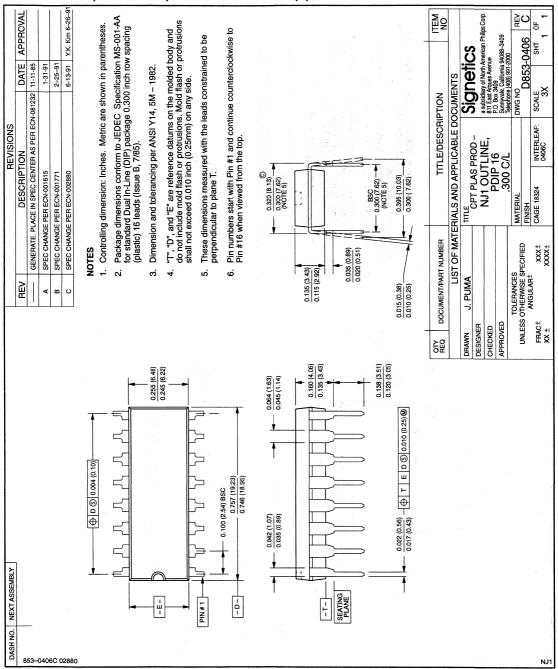

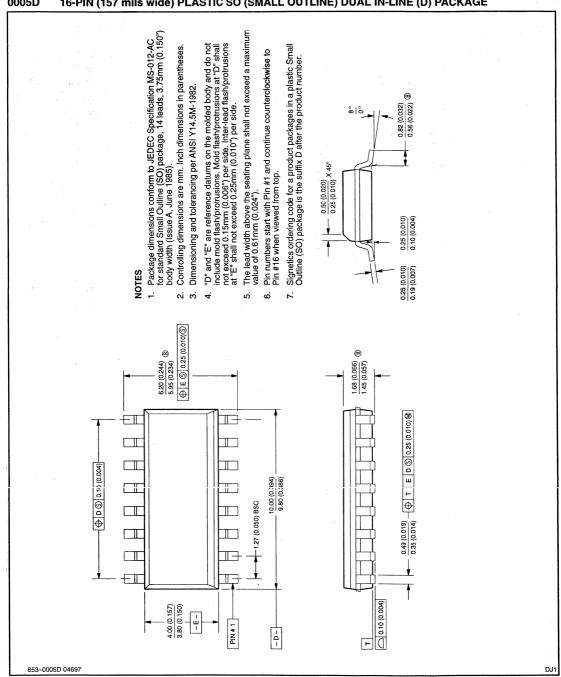

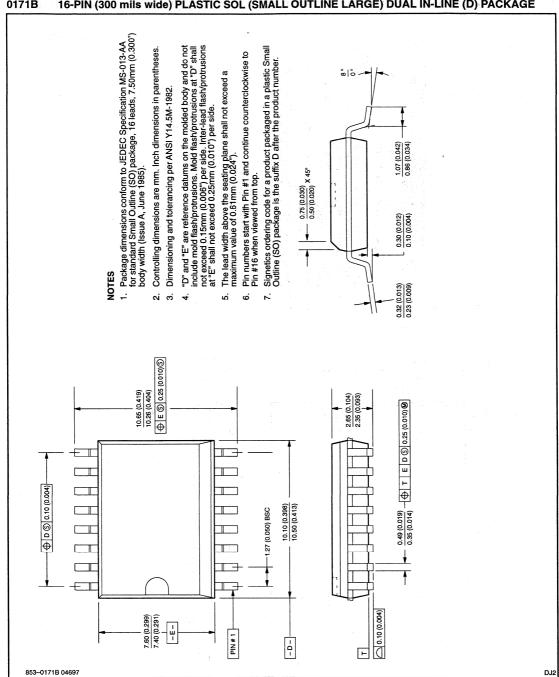

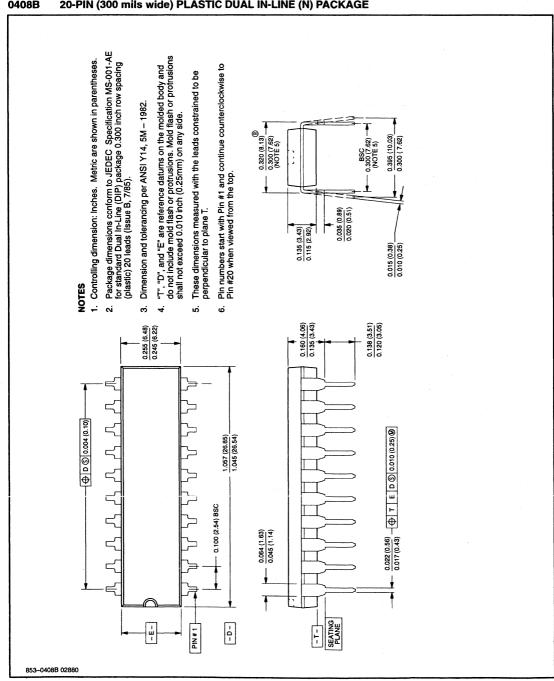

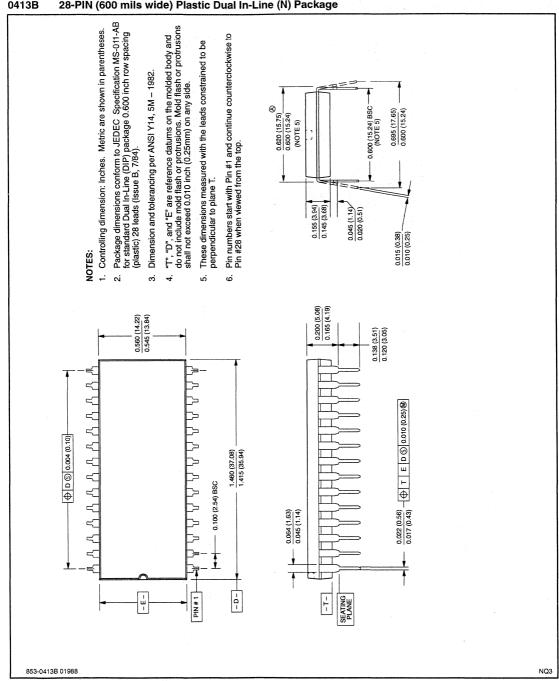

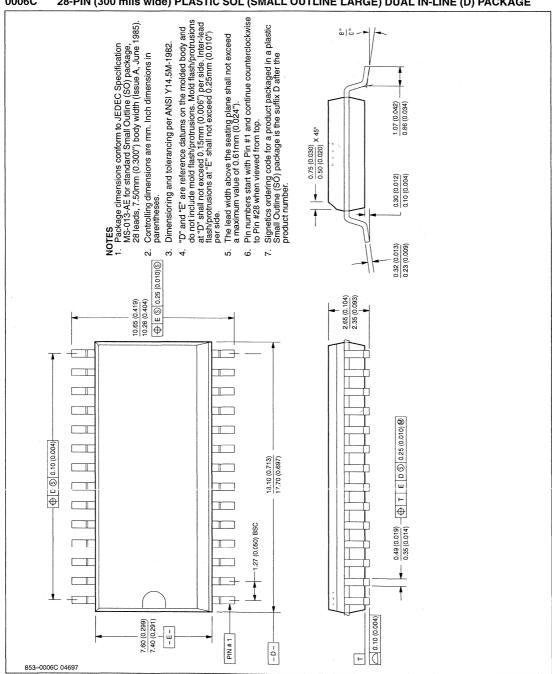

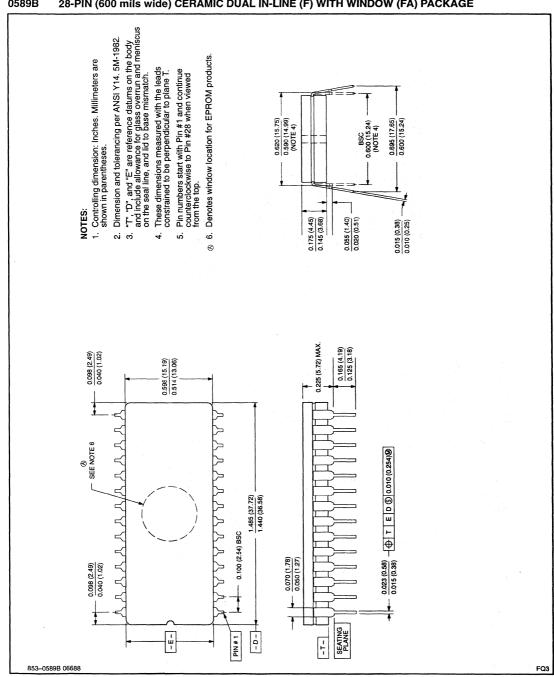

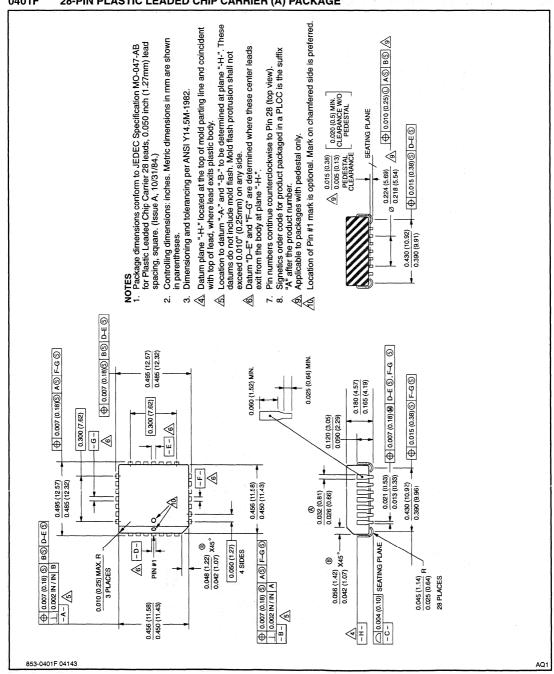

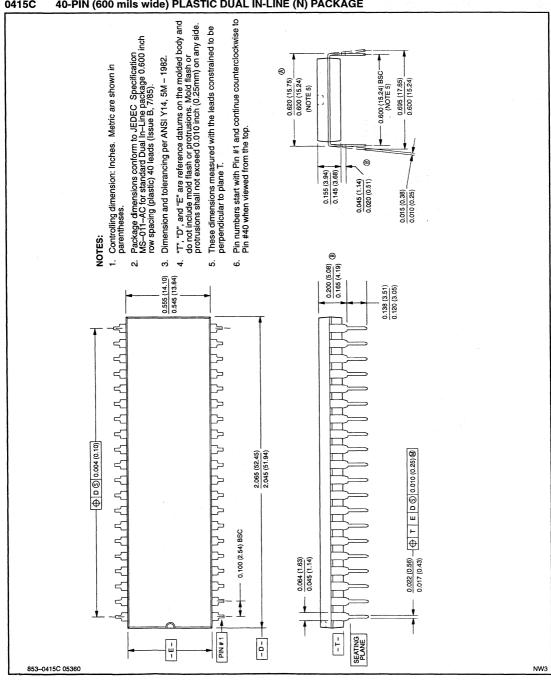

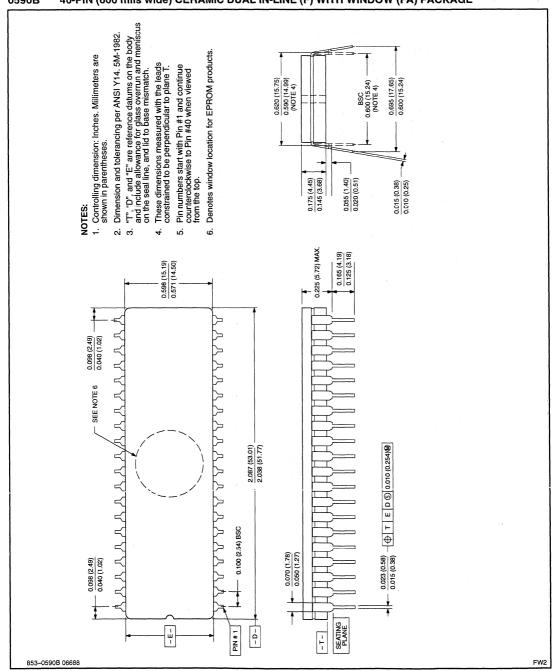

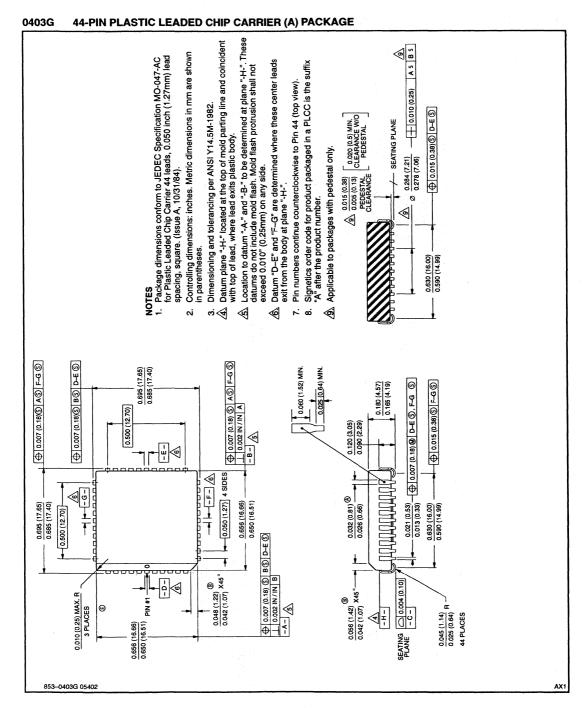

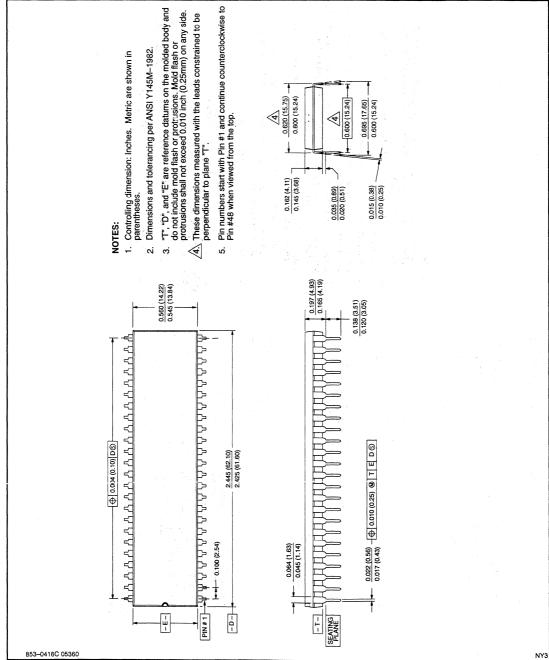

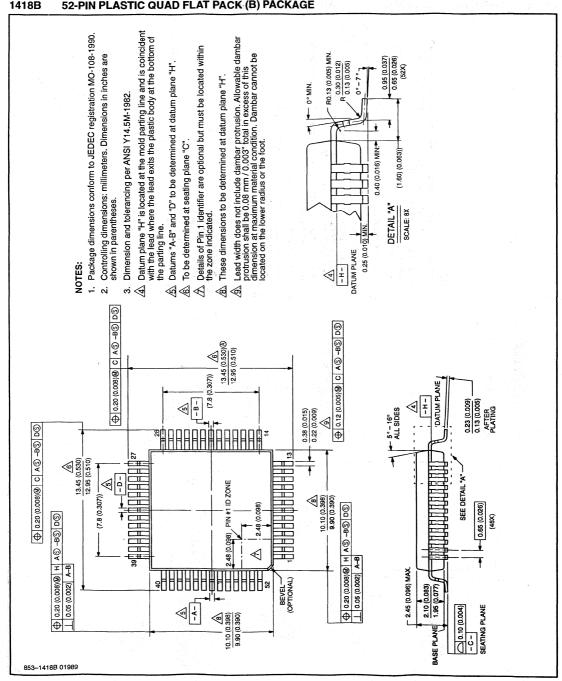

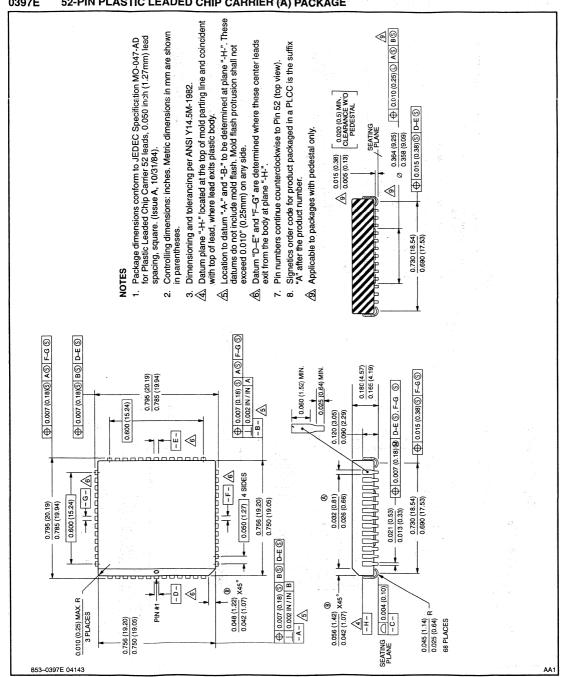

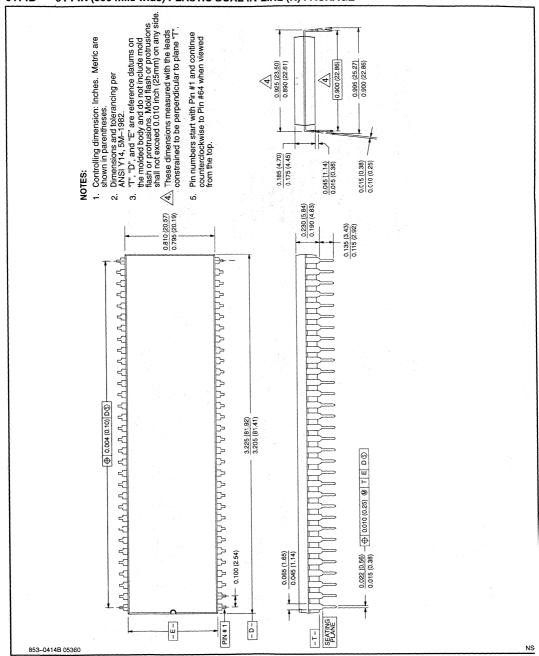

| Section 8 Packa    | ge Outlines                                                                    | 969  |

| List of package or | utline drawings                                                                | 969  |

| Soldering          |                                                                                | 995  |

| Section 9 Sales    | Offices                                                                        | 997  |

| North American S   | Cales Offices, Representatives and Distributors                                | 999  |

| Appendix A Data H  | landbook System                                                                | 1000 |

# **Alphanumeric Product List**

| AM26LS31         | Quad high-speed differential line driver                                      | 685 |

|------------------|-------------------------------------------------------------------------------|-----|

|                  | Quad high-speed differential line receivers                                   | 690 |

| AM26LS32B        | Quad high-speed differential line receivers                                   | 693 |

| FB2012A          | Futurebus+ central arbitration controller                                     | 919 |

| FB2031           | 9-bit latched/registered/pass-thru Futurebus+ transceiver                     | 928 |

| FB2033           | 8-bit latched/registered/pass-thru Futurebus+ universal interface transceiver | 941 |

| FB2040A          | 8-bit Futurebus+ transceiver                                                  | 951 |

| FB2041           | 7-bit Futurebus+ transceiver                                                  | 959 |

| MC145406         | EIA-232-D/V.28 driver/receiver                                                | 669 |

| NE5050           | Power line modem                                                              | 696 |

| NE5080           | High-speed FSK modern transmitter                                             | 702 |

| NE5081           | High-speed FSK modem receiver                                                 | 707 |

| NE5170           | Octal line driver                                                             | 674 |

| NE5180/NE5181    | Octal differential line receiver                                              | 680 |

| NE5210           | Transimpedance amplifier (280MHz)                                             | 819 |

| NE8392A          | Coaxial transceiver interface for Ethernet/Thin Ethernet                      | 710 |

| NE8392C          | Coaxial transceiver interface for Ethernet/Thin Ethernet                      | 719 |

| NE8392C-2        | Coaxial transceiver interface for Ethernet/Thin Ethernet                      | 728 |

| NE83Q92          | Low-power coaxial Ethernet transceiver                                        | 755 |

| NE83Q93          | Enhanced coaxial Ethernet transceiver                                         | 765 |

| NE83C92          | Low-power coaxial Ethernet transceiver                                        | 776 |

| NE83Q94          | Miniature coaxial Ethernet transceiver                                        | 785 |

| NE86C92          | Twisted-pair transceiver interface                                            | 737 |

| NE/SA5211        | Transimpedance amplifier (180MHz)                                             | 832 |

| NE/SA5214        | Postamplifier with link status indicator                                      | 861 |

| NE/SA5217        | Postamplifier with link status indicator                                      | 867 |

| NE/SA5224        | FDDI fiber optic postamplifier                                                | 896 |

| NE/SA5225        | Fiber optic postamplifier                                                     | 901 |

| NE/SA/SE5212A    | Transimpedance amplifier (140MHz)                                             | 847 |

| SA5222           | Low-power FDDI transimpedance amplifier                                       | 874 |

| SA5223           | Wide-dynamic-range AGC                                                        | 893 |

| SCC2691          | Universal asynchronous receiver/transmitter (UART)                            | 176 |

| SCC2692          | Dual asynchronous receiver/transmitter (DUART)                                | 195 |

| SCC2698B         | Enhanced octal universal asynchronous receiver/transmitter (Octal UART)       | 336 |

| SCC68692         | Dual asynchronous receiver/transmitter (DUART)                                | 222 |

| SCN2651          | Programmable communications interface (PCI)                                   | 60  |

| SCN2652/SCN68652 | Multi-protocol communications controller (MPCC)                               | 75  |

| SCN26562         | Dual universal serial communications controller (DUSCC)                       | 413 |

| SCN2661/SCN68661 | Enhanced programmable communications interface (EPCI)                         | 97  |

| SCN2681          | Dual asynchronous receiver/transmitter (DUART)                                | 116 |

| SCN2681T         | Dual asynchronous receiver/transmitter (DUART)                                | 143 |

| SCN68562         | Dual universal serial communications controller (DUSCC)                       | 430 |

| SCN68681         | Dual asynchronous receiver/transmitter (DUART)                                | 154 |

| SC26C198         | Octal universal asynchronous receiver/transmitter (UART)                      | 371 |

| SC26C562         | CMOS dual universal serial communications controller (CDUSCC)                 | 456 |

| SC26C92          | Dual universal asynchronous receiver/transmitter (DUART)                      | 248 |

| SC26C94          | Quad universal asynchronous receiver/transmitter (QUART)                      | 271 |

| SC68C562         | CMOS Dual universal serial communications controller (CDUSCC)                 | 474 |

| SC68C94          | Quad universal asynchronous receiver/transmitter (QUART)                      | 302 |

|                  |                                                                               |     |

#### **Philips Semiconductors**

# **Product Status**

ICs for Data Communications

#### **DEFINITIONS**

| Data Sheet<br>Identification | Product Status         | Definition                                                                                                                                                                                                                                    |

|------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective Specification      | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                            |

| Preliminary Specification    | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product Specification        | Full Production        | This data sheet contains Final Specifications. Signetics reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |

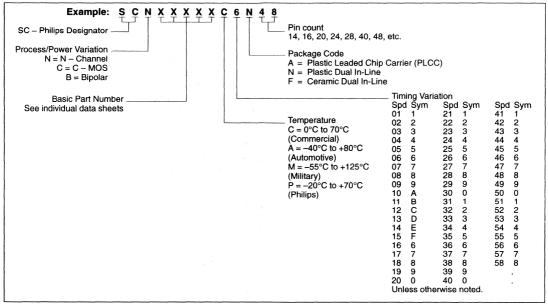

## **Ordering information**

#### **DATA COMMUNICATIONS CONTROLLERS**

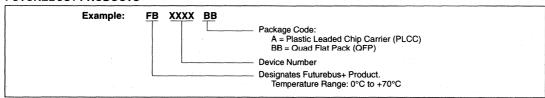

#### **FUTUREBUS+ PRODUCTS**

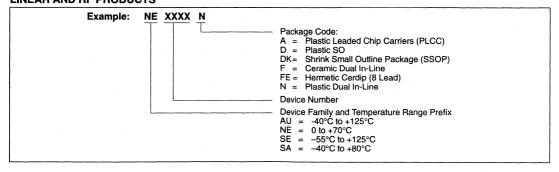

#### LINEAR AND RF PRODUCTS

#### Α

Access method: A software/hardware method of transferring data between host-resident application programs and remote devices. This term is usually used to describe communications software residing in a mainframe computer.

ACK or acknowledge: A character or sequence of characters sent by a receiver to notify a sender that the last message was received correctly. ACK is also sent by a remote device as a "go-ahead" response to a selection sequence.

**Acoustic coupler:** A type of modern that permits use of a telephone handset as a connection to the public telephone network for data transmission by means of sound transducers.

Adaptive differential pulse code modulation: One of the methods of pulse code modulation utilized in digitizing an analog signal (32 Kbps is typical).

**Adaptive equalization:** A modem feature allowing it to automatically compensate for distortions on the line.

Adaptive predictive coding: A methodology used in compressing digitized voice signals.

**Algorithm:** A prescribed set of well—defined rules or processes for arriving at a solution to a problem. A mathematical process.

**Alphanumeric:** Made up of letters (alphabetic) and numbers (numeric).

**Alternative route:** A secondary communications path used to reach a destination if the primary path is unavailable.

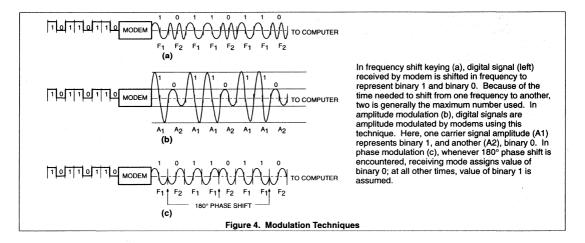

Amplitude modulation: Transmission of information on a communications line by varying the voltage level or amplitude.

**Ambient noise:** Signal interference that is present on a communications line at all times (background noise).

**Amplifier:** A device that increases the power or amplitude of a signal.

Amplitude variation (ripple): Unwanted variation of signal voltage at different frequencies on a communications line.

**Analog signal:** A signal that changes in a non-discrete manner (smooth transitioning to different levels).

**Answer back:** A transmission from a receiving data processing device in response to a request from a transmitting data processing device that it is ready to accept or has received data.

ARQ, Automatic re-transmission request: A generic description of a protocol mechanism that involves re-transmission of message blocks received in error. There are several types of ARQ operation.

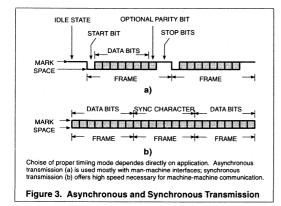

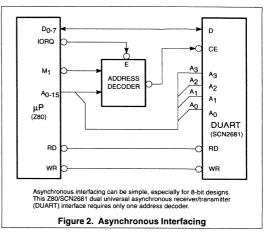

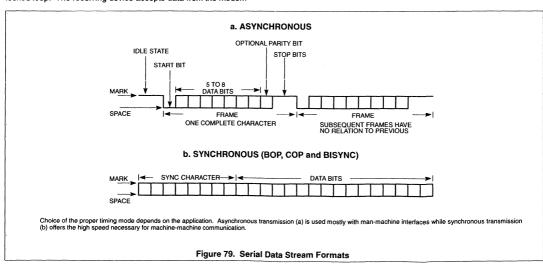

**Asynchronous:** A data transmission which does not require a separate clock signal for the reception of data. In code sets, character codes containing start and stop bits.

Asynchronous transmission (start—stop transmission): Provides transmission of one character at a time with a start bit and one or more stop bits appended on each one. Any amount of time can elapse before the next character can be sent.

Attenuation: Loss of communication signal energy.

Audio frequencies: Frequencies that can be heard by the average human ear, usually between 15 and 20,000 Hz.

**Automatic dialer:** A device that will automatically dial telephone numbers on the network. Operation of the dialer may be manual or automatic.

#### R

Backward channel (also called reverse channel): A channel used for sending data in the opposite direction of the primary (forward) channel. The backward channel is usually used for sending data at low speeds for either control purposes or keyboard data.

**Balanced circuit:** A circuit terminated by a network whose impedance balances the impedance of the line so that the return losses are negligible.

**Bandwidth:** The information carrying capability of a communications channel or line.

Baseband: The frequency band occupied by individual information bearing signals before they are combined with a carrier in the modulation process. In LANs, one transmitting device at a time on the circuit.

**Base group:** Twelve communications paths capable of carrying the human voice on a telephone set. A unit of frequency-division multiplexing systems bandwidth allocation.

**Baud:** Data communication rate unit taken from the name Baudot. Defined as the number of signal level changes per second regardless of the information content of those signals.

**Baudot:** A five-level code set named for the early French telegrapher who invented it. International Telegraph Alphabet (ITA) Number 2 is the formal name.

Bias: Communications signal distortion with respect to bit timing.

Bit: Binary digit contraction. The smallest unit of data communications information, used to develop code representations of phenotetre.

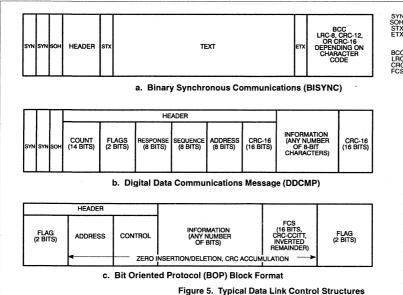

**Bit-oriented protocol:** Refers to those data communications protocols that move bits across a data link without regard to the meaning of those bits. Nearly all bit-oriented protocols follow the international HDLC recommendations.

Bit rate: The rate at which bits (binary digits) are transmitted over a communications path. Normally expressed in bits per second (BPS). The bit rate is not to be confused with the data signaling rate (baud), which measures the rate of signal changes being transmitted.

Bit stream: Refers to a continuous series of bits being transmitted on a transmission line.

**Blank:** A condition of "no information" in a data recording medium or storage location, which can be represented by all spaces or all zeros, depending on the medium.

**Block error rate testing:** Testing a data line with groups of information arranged into transmission blocks for error checking.

**Block:** Some set of contiguous bits, bytes, or both that make up a definable quantity of information.

**Block check character:** A single character appended to the end of a data block for error-checking purposes. The BCC is usually LRC but could also be checksum results.

Blocked Asynchronous/Synchronous Transmission: A proprietary software package for sending asynchronous and synchronous information used primarily by personal computer interfaces.

**Blocking:** A condition in a switching system or PBX in which no paths or circuits are available to complete a call and no dial tone is

returned to the calling party. In this situation there is no alternative but to hang up and try the call again. Also referred to as denial or busy condition.

**Block multiplexer channel:** A computer peripheral multiplexer channel that interleaves blocks of data. See also Byte multiplexer channel. Contrast with selector channel.

**Break:** A signal used to "break in" when the opposite party or unit is sending. A feature of dial point-to-point teletypewriter systems operating in half duplex.

Breakout box: A test device utilized for monitoring and inserting signals at the RS-232 interface. Bridge Equipment and techniques used to connect circuits and equipment to each other ensuring minimum transmission impairment. Bridging is normally required on multipoint data channels where the drop for the local loop is separated from the circuit that continues on to the next drop.

**Broadband:** Refers to transmission facilities whose bandwidth (range of frequencies they will handle) is greater than that available on volce-grade facilities; sometimes called wideband. Also used to describe a particular kind of local area network configuration where multiple different users can share the same cable facility in different channels.

**Broadcast:** The ability to send messages or communicate with many or all points on a circuit simultaneously.

Burst: A series of events occurring as a group.

**Burst error:** A series of consecutive errors in data transmission. Refers to the phenomenon on communication lines where errors are highly prone to occurring in groups or clusters.

**Bus:** A single connective link between multiple processing sites (co-located only) where any of the processing sites can transmit to any other but only one way at a time.

Byte: Some set of contiguous bits that make up a discrete item of information. Bytes are 8 bits long.

Byte multiplexer channel: Multiplexer channel that interleaves bytes of data from different sources. Contrasts with selector channel.

**Call forwarding:** Calls to one station can be automatically switched to another specified station.

**Call setup time:** The overall length of time required to establish a switched call between pieces of data terminal equipment.

Camp-on: A feature of a switching station or device that notifies a calling station that a called station is busy and allows the calling station to wait and be automatically connected when the line is free.

Carrier: An analog signal at some frequency modified by information (changes to frequency or amplitude or phase or combinations of amplitude and phase) to represent that data in a communication system.

Carrier system: A method of obtaining or deriving several channels from one communication path by combining them at the originating end, transmitting a wideband or high-speed signal, and then separating the original information at the receiving end.

Centrex: A type of private branch exchange service where the equipment is physically located in the local telephone exchange.

Chain: A series of processing locations that information must pass through each location on a store-and-forward basis in order to get to a final location.

Channel: A data communication path.

**Channel bank:** Communication equipment performing multiplexing. Typically used for multiplexing voice-grade channels.

Character: A language unit composed of bits.

Character parity: A technique of adding an overhead bit to a character code to provide error-checking capability.

Character synchronization: The process through which a receiving device can determine which bits, sent over a data link, should be grouped together into characters.

**Checksum:** A BCC or BCS that is computed using simple binary addition.

Circuit: The electrical path that provides communication between two or more locations.

Circuit switching: A method of communication in which an electrical connection between calling and called stations is established on demand for exclusive use of the caller until the connection is released.

Clocking: Time synchronizing of communication information.

**Cluster:** A group of user terminals co-located and connected to a single controller through which each terminal is afforded the opportunity to access a single communication line.

**Cluster controller:** An intelligent device, usually located at a remote site, that allows several "dumb" terminals or similar devices to connect to a single modem on a data link.

**Coaxial cable:** Cable with a shield against noise around a signal–carrying conductor.

**CODEC, Coder/Decoder:** A device for digitizing a voice signal or converting the digitized signal back to voice. Performs the opposite function of a modem.

**Communication line controller:** A hardware unit that performs line control functions with the modem.

Compandor: A device used on some telephone channels to improve transmission performance. The equipment compresses the outgoing speech volume range and expands the incoming speech volume range on a long—distance telephone circuit.

Concentrator: An electronic device that interfaces in a store and forward mode with multiple communication lines at a message level and then re-transmits those messages via one or more high-speed communications lines to a processing site.

**Conditioning:** A technique of modifying electrical circuit parameters on a communication line to improve the capability of that line to support higher data transmission rates. (See Equalization.)

**Contention:** User competition for use of the same communications facilities; a method of line control in which terminals request or bid to transmit. If the channel is not free, the terminals must wait until it is.

**Control character:** A character that is normally non-printable and used for control purposes rather than for the exchange of information.

Controlled carrier: A feature of a modem that allows the modem carrier signal to be turned on or off under command of the DTE. A controlled carrier is necessary at remote locations on multipoint lines.

**CRC, cyclic redundancy check:** An error-checking control technique utilizing a specifically binary prime divisor that results in a unique remainder.

CSMA/CD, carrier sensed multiple access/collision detection: A method of transmitting information in the local area network environment (LAN) where only one transmitter may be on the line at any one time. If two devices transmit simultaneously, the signals "collide" and both must cease transmission. Each will try again at a later time determined by a different internal delay.

CTS, clear to send: A control line between a modem and a controller used to operate over a communication line.

**Current loop:** An interface in which the absence or presence of current now (as opposed to voltage levels) is used to provide signaling between devices.

**Cursor:** A lit area on an electronic display screen used to indicate the next character location to be accessed.

#### D

**Data compression:** The technique that provides for the transmission of fewer data bits without the loss of information. The receiving location expands the received data bits into the original bit sequence.

**Data set (modem):** An electronic terminating unit for analog lines used for data signal modulation and demodulation.

**dBm:** Power level measurement unit in the telephone industry. 0 dBm is 1mW at 1004 Hz terminated by  $600\Omega$  impedance.

Decibel (dB): Power level measurement unit.

**Dedicated line:** A communication line that is not dialed. Also called a leased line or private line.

**Delay:** A period of time that elapses between the end of one event and the start of another.

**Delay distortion:** A distortion that occurs on communication lines due to the different propagation speeds of signals at different frequencies. Some frequencies travel more slowly than others in a given transmission medium and therefore arrive at the destination at slightly different times. Delay distortion is measured in microseconds of delay relative to the delay at 1200 Hz. Delay distortion does not affect voice, but it can have a serious effect on data transmissions.

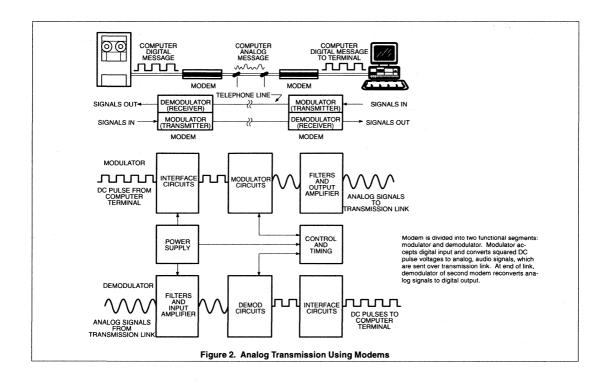

**Demodulator:** A functional section of a modem that converts the received analog line signals back to digital form.

Dial line: A communication line that is dialed.

Digital: A two-discrete-state signal.

**Distortion:** The unwanted modification or change of signals from their true form by some characteristic of the communication line or equipment being used for transmission (such as delay distortion, amplitude distortion).

**DPCM, differential pulse code modulation:** A method of digitizing an analog signal.

**Drop outs:** On a communication line, the signal can temporarily disappear, causing loss of data. Drop outs are often caused by environmental influences such as lightning.

E

**Echo distortion:** A telephone line impairment caused by electrical reflections at distant points where line impedances are dissimilar.

**Echoplex:** An error-detection method in which characters sent by a terminal to a host are sent back to the terminal and displayed.

Echo suppressor: A device installed in long-distance telephone lines for eliminating echo back to the speaker. Echo suppressors can cause difficulties with simultaneous two-way communications unless they are disabled by the modems.

**Emulation:** The act of imitating or performing as if a device or program were something else.

**Encryption:** The technique of modifying a known bit stream on a transmission line so that it appears to be a random sequence of bits to an unauthorized observer.

**End office:** The first telephone office that a data line is connected to over the local loop or access line. The end switching office for a dialed connection.

**Envelope delay:** An analog line impairment where a variation of signal delay with frequency occurs across the data channel bandwidth (see Delay distortion).

**Equalization:** A technique used to compensate for distortions present on a communication channel.

**Error rate:** The number of errors per unit of information in the test to establish the error rate.

F

FDM, frequency-division multiplexing: A multiplexing technique with which a data line bandwidth is divided into different frequency sub-channels used to share a data line between several user terminals

Fiber-optics: Glass fibers that carry visible light containing information in cables.

Filter: Electronic circuitry that blocks some components of a signal while allowing other components to pass through uniformly. For example, a high-pass filter blocks all frequencies in a signal that are below a specified frequency called the "cut off."

**Firmware:** A set of software instructions set permanently or semi-permanently into a read-only memory.

**Fixed equalization:** A simple equalization technique for modems by which the amount of compensation is preset internally or externally to the modem.

Flag: A bit field or character of data used to set apart the data on either side of the flag. A delimiter.

Flow control: A procedure by which a sending station can be "throttled" so that it does not send more data into the data link or network than can be handled by the link or network.

FM, frequency modulation: A method of transmitting digital information on an analog line by changing the carrier frequency between two different values.

Format: A structure of a message or data such that specific controls or data can be identified by their position during processing.

Forward error correction: The technique that provides for the transmittal of additional information with the original bit stream so that if an error is detected the correct information can be recreated at the receive end without a re-transmission.

**Four-wire circuit:** A circuit that consists of two twisted pair cables. A four-wire circuit provides two separate circuits between stations.

Frame: Bit—oriented protocols refer to data blocks as frames. Also, in T-1 transmissions, 8 bits from each of 24 channels plus 1 frame bit for a total of 193 bits

**Frequency:** The number of cycles of an alternating current signal per unit time.

Frequency shift keying, FSK: A form of frequency modulation in which the carrier frequency is made to vary or change in frequency at the instant there is a change in the state of the signal being transmitted (the carrier frequency on the line during a one or marking condition would be shifted to another predetermined frequency during a zero or spacing condition).

Frequency stacking: Another name for FDM, which indicates how the multiplexing is performed.

Front end: An auxiliary computer system that performs network control operations, freeing the host computer system to do data processing.

**Full duplex:** A four-wire circuit, or a protocol that provides for transmission in both directions at the same time between the same two points.

Full-duplex modem: Provides a channel for sending data in each direction. Full-duplex modems are required for two stations to send data to each other at the same time.

#### G

**Gain:** The degree to which the amplitude of a signal is increased. The amount of amplification realized when a signal passes through an amplifier or repeater. Normally measured in decibels.

Gaussian noise: A noise whose amplitude is characterized by the Gaussian distribution, a well known statistical distribution (white noise, ambient noise, hiss).

Geosynchronous: A communication satellite orbit at the correct distance from earth and at the correct speed to appear fixed in space as the earth rotates.

Gigahertz (GHz): An analog frequency unit equal to 1 billion Hz.

**Go-back-N:** A form of continuous ARQ in which all blocks or frames following a block received in error are discarded and need to be resent.

**Group address:** Used to address two or more stations in a predesignated group.

**Guardband:** The unused frequency band between two channels that provides separation of the channels to prevent mutual interference.

#### Н

**Half duplex:** A communication line consisting of two wires or a protocol capable of transmitting only one direction at a time.

**Handshaking:** Line termination interplay to establish a data communication path.

**Harmonic:** Frequencies that are multiples of some fundamental frequency.

**Harmonic distortion:** A data communications line impairment caused by erroneous frequency generations along the line.

**High-level data link control:** An ISO standard data communications line protocol.

**Hertz:** Internationally recognized unit of measure for electrical frequency. The number of cycles per second. Abbreviated Hz.

**House cables:** Conductors within a building used to connect communications equipment to termination blocks.

**Hybrid:** An inductive device that converts a two-wire circuit into a four-wire circuit or a four-wire circuit into a two-wire circuit.

ı

**Impedance**: The total opposition offered by a component or circuit to the flow of an alternating or varying current; a combination of resistance, capacitance, and inductance.

Impulse noise: A type of interference on communication lines characterized by high amplitude and short duration. This type of interference may be caused by lightning, electrical sparking action, or by the make-break action of switching devices.

**Insertion loss:** Signal power loss due to connecting communication equipment units with dissimilar impedance values.

**Integrity of data:** The status of information after being processed by software or transmitted over a communication link.

Interference: Refers to unwanted occurrences on communications channels that are a result of natural or man-made noises and signals, not properly a part of the signals being transmitted.

Intermodulation distortion: An analog line impairment where two frequencies create an erroneous frequency, which in turn distorts the original data signal representation.

**Isochronous:** The term given to the movement of start-stop data (asynchronous transmission) over a synchronous data link with each intervening time interval being an integral number of character times.

J

Jitter: Type of analog communication line distortion caused by the variation of a signal from its reference timing positions, which can cause data transmission errors, particularly at high speeds.

Κ

L

Leased line, private line, dedicated line: A communications line, usually a four-wire circuit, for voice, data, or both leased from a communications carrier on a monthly basis.

**Line driver:** An inexpensive amplifying device that allows two or more devices to communicate over inexpensive twisted-pair cable up to 2000 feet and up to 19,200 BPS.

**Loading coils:** Inductive devices that improve the quality of voice transmissions (distorts data signals and must therefore be compensated for by standard modems).

**Local loop:** The access line from either a user terminal or a computer port to the first telephone office along the line path (also called station loop, end loop, or subscriber loop).

**Logging:** The act of recording something for future reference, such as error events or transactions.

**Loopback:** Directing signals back toward the source at some point along a communications path.

**Loop current:** A teletypewriter-to-line interface and operating technique that involves switching an electrical current on and off to represent data bits.

#### М

Mark: Interface standards define a mark to be the condition of the data line when sending a logic one.

Megahertz, MHz: A unit of analog frequency equal to 1 million Hz.

Message switching: Routing messages among three or more locations by store-and-forward techniques in a computer.

Metallic circuits: Refers to circuits that use metal wire (copper) from end to end. Implies that no loading coils or any other devices are interposed between the ends of the circuit. Metallic circuits have electrical (DC) continuity from end to end.

**Microcode:** A set of software instructions that executes a macro instruction.

**Microwave:** A radio carrier system using frequencies whose wavelengths are very short.

**Milliampere, mA:** Electric current measurement unit equal to 0.001 Ampere.

Milliwatt, mW: A power unit of measurement equal to 0.001 watt.

**Modem (data set):** An acronym taken from functions the unit performs by modulating and demodulating the digital information from a terminal or computer port into an analog carrier signal to be sent over an analog line.

**Modem eliminator:** A device that allows two DTE devices to be connected without using modems.

**Modem sharing unit:** A device that allows several terminals or other devices to share a single modem.

**Multiplexer:** A device that accepts many data lines and combines them into a single high-speed, composite data stream.

**Multipoint line:** Also called a multidrop line. A communications line having several subsidiary controllers that share time on the line under control of a central site.

**Multistation controller:** A terminal controller having more than one terminal device connected to it for subsequent access to the communication line.

#### N

Narrowband: Refers to a LAN configuration in which only one user can transmit at any one time (sometimes called baseband).

**Noise:** A communications line impairment that is inherent in the line design or induced by transient bursts of energy.

#### О

Octet: A group of eight bits that usually, though not necessarily, represents a byte, or word, and so on.

#### Р

Packet switching: The transfer of data by means of addressed packets whereby a channel is only occupied for the duration of transmission of the packet. The channel is then available for the transfer of other packets.

PAD, packet assembler/disassembler: Equipment providing packet assembly and disassembly facilities.

Parity error: An error that occurs in a particular entity of data in which an extra or redundant bit is sent with the data. Detects only odd numbers of bit errors. Even numbers of bit errors are not detected.

Pass-band filters: Filters used in modem design to allow only the frequencies within the communication channel to pass, while rejecting all frequencies outside the pass band.

Patching jacks: Series-access devices used to patch around faulty equipment using spare units.

Private branch exchange: A telephone switchboard.

**PCM**, **pulse code modulation**: A generic method of converting an analog signal to a digital form.

**Phase hits:** A sudden electrical disturbance on a communication line which causes the phase of the carrier signal to change, causing bit errors on the data link.

**Phase jitter:** An analog line impairment caused by power and communication equipment along the line, shifting the signal phase relationship back and forth.

PM, phase modulation: A method of combining digital information onto a line-carrying signal by variation of the phase relationship of the signal. May also indicate preventive maintenance in the form of service functions provided during periods of normal operation to reduce the probability of failure later on.

**Point to point:** A communications line connected directly from one point to another, as opposed to multipoint lines.

**Polling:** A control message sent from a master site to a slave site as an invitation for the slave site to transmit data to the master site.

**Propagation delay:** The time necessary for a signal to travel from one point on the circuit to another.

**Protocol:** A formal set of conventions governing the format and control of inputs and outputs between two communicating processes. Includes handshaking and line discipline.

PSK, phase shift keying: A method of analog modulation utilizing differences in phase only as representing data bit one of several ways to represent an analog signal. Typical methods involve modifying the amplitude (PAM), width or duration (PDM), or position (PPM). The most common pulse modulation technique in telephone work is pulse code modulation (PCM). In PCM, the analog signals are sampled at regular intervals and a series of binary bits representing the amplitude of each pulse is transmitted, representing the amplitude of the information signal at that time. The standard sampling in today's environment is 8000 times per second with 8 binary bits representing each sample pulse giving a required transmission rate of 64,000 BPS.

#### Q

**QAM, quadrature amplitude modulation:** A method of modulation in which two carriers in quadrature are used for modulation. One carrier is used for modulating the X axis and the other carrier is used for modulating the Y axis.

**Quadrature distortion:** Analog signal distortion frequently found in phase modulation modems.

#### R

Regenerative repeaters: A device interposed between the ends of a data link or between nodes of a network to regenerate distorted signals. Used in digital transmission.

**Response time:** The time measured from the depression of the enter key at a terminal to the display of the first character of the response at that terminal site.

Reverse channel: An optional feature provided on some modems that provides simultaneous communication from the receiver to the transmitter on a two-wire channel. It may be used for circuit assurance, circuit breaking, and facilitating certain forms of error control and network diagnostics. Also called backward channel.

RTS, request to send: An RS-232 control signal that requests a data transmission on a communication line.

S

SDLC, synchronous data link control: An IBM data communications message protocol. A subset of HDLC.

**Slicing level:** A voltage or current level of a digital signal that determines whether a one or zero bit will be recognized.

**Slot:** A unit of time in a TDM frame in which a sub-channel bit or character is carried to the other end of the circuit and extracted by the receiving TDM unit.

S/N, signal-to-noise ratio: The relative power levels of a communication signal and noise on a data line, expressed in decibels

Space-division multiplexing: Refers to using a separate circuit or channel for each device. Essentially this means no multiplexing at all. If, for example, a new terminal needs to be added to a system, a separate wire is run to accommodate it.

Start bit: In asynchronous transmission, the start bit is appended to the beginning of a character so that the bit sync and character sync can occur at the receiver. The start bit is always a "0" or "space" condition.

**Start-stop:** Also known as asynchronous transmission. A transmission technique in which each character is preceded by a start bit and followed by a stop bit.

**Stop-and-wait ARQ:** A form of ARQ in which the sender sends one block of data and stops sending until an acknowledgment for that block is received from the receiver. An example is bisync.

Stop bit: In asynchronous transmission, the stop bit is appended to the end of each character. The stop bit is always a "1" or "mark" condition. It sets the receiving hardware to a condition where it looks for the start bit of a new character. May be 1 or 2 bits.

Store and forward: A data communication technique that accepts messages or transactions, stores them until they are completely in the memory system, and then forwards them to the next location as addressed in the message or transaction header.

**Streaming:** A condition of a remote modem when it is sending a carrier signal on a multi-drop communication line and will not turn off.

**String coding:** A technique for combining multiple sequential occurrences of the same character or bits.

**Switched service:** A common carrier communications service that requires that call establishment take place before a data link can be established. For example, DDD is a switched service.

**Sync (syn):** A bit or character used to synchronize a time frame in a TDM. Also a synchronizing sequence used by synchronous

modems to perform bit synchronization and by the line controller for character synchronization.

**Synchronous modem:** A DCE that utilizes a clocking signal to perform bit synchronization with the incoming data.

Synchronous transmission: Messages sent in blocks where all characters or bits are sent contiguously. No start or stop bits are appended to characters. Each block begins with a sync sequence and a start of message sequence so that character framing can occur at the receiver and ends with an end of message sequence to prepare the receiver to look for a new message.

1

**Tariff:** The rates, rules, and regulations concerning specific equipment and services provided by a communications carrier.

**T-Carrier:** The AT&T name for their digital carrier system used for carrying data or digitized voice signals.

**TDMA**, time division multiple access: A method utilized primarily in satellite transmission in which various users share their time on the same satellite link (portions of separate users are multiplexed onto the same link through a satellite).

**Telemetry:** Collection and transmission of data obtained from remote locations by sensing conditions in a real-time environment.

**Telex:** A teletypewriter service that allows subscribers to send messages to other subscribers on an international level over the public telephone network.

Terrestrial circuits: Non-satellite channels.

**Text:** That part of a message or transaction between the control information of the header and the control information of the trace section or tail that constitutes the information to be processed or delivered to the addressed location.

**Thermal noise:** A type of electromagnetic noise produced in conductors or in electronic circuitry that is proportional to temperature. See also Gaussian noise.

Time-division multiplexing, TDM: A technique for combining several information channels into one facility or transmission path in which each channel is allotted a specific position in the signal stream based on time. At the receiving end, the signals are separated to reconstruct the individual input channels.

**Time-out:** A protocol procedure that requires a device to make some response to a command or message block within a certain period of time. If the response does not occur within that period of time, a time-out condition occurs, which is considered an error condition.

**Time sharing:** A processing technique by which multiple users at their own remote terminals have the ability to share common computer resources at the same time.

**Trailer or trace block:** Control information transmitted after the body or text of a message or transaction used for tracing error events, timing the communications through the network, and recovering misplaced blocks or transactions after system failures.

**Transparency:** A transmission mode achieved when both the sending and receiving devices do not react to the content of the data they are sending.

**Trunk:** A multiple line circuit that connects two switching or distribution stations or centers. Also a circuit from a PBX to a Class 5 telephone office.

**Turnaround time:** The time required for a modem to reverse direction of transmission on a two-wire circuit.

Validity checking: The techniques used to check the accuracy of data after transmission on data lines.

VF, voice frequency or voice-grade line: A 4.2kHz bandwidth telephone channel designed to carry the human voice from one telephone set to another. The usable portion of the band is 300 Hz to 3300 Hz.

**VHF, very high frequency:** A radio carrier frequency band used in radio transmissions.

VRC, vertical redundancy checking: A method of character parity checking.

WATS, Wide Area Telephone Service: A flat rate or measured bulk rate long-distance telephone service provided on an incoming or outgoing basis. By use of an access line, WATS permits a customer to make telephone calls to any dialable telephone number in a specific zone for an hourly rate. INWATS permits reception of calls from specific zones over an access line in like manner but the called party is charged with the call. The United States has been divided into five zones of increasingly greater coverage depending on the location of the customer.

White noise: See Gaussian noise; Thermal noise.

**Wideband:** In LAN systems, the ability for multiple users to communicate simultaneously in different channels. Same as broadband.

**Word:** One or more contiguous bytes, which may also be used to identify a class of computer.

#### **NETWORK STANDARDS**

Three types of Network Standards are described here. The first will be the Electronic Industries Association (EIA) specifications, which are always preceded by the letters RS (Recommended Standard) or EIA. The second set will be the CCITT standard interface specifications, which are always preceded by the letter V, and the third series of specifications, also established by the CCITT, are always preceded by the letter X. A V specification deals primarily with telephone circuits, while the X specifications deal primarily with data interfaces and public data networks. The most common specifications in use today are identified below.

EIA-232-D. Interface between data terminal equipment and data communication equipment employing serial binary data interchange (January 1987).

**EIA-269–B.** Synchronous signaling rates for data transmission (January 1976; identical to ANSI X3.1–1976).

EIA-334-A. Signal quality at interface between data processing terminal equipment and synchronous data communication equipment for serial data transmission (August 1981) (also adopted as ANSI X3.24-1967).

**EM-334-A-1.** Addendum No. 1 to EIA-334-A and EIA-404. Application of signal quality requirements to EIA449.

EIA-357. Interface between facsimile terminal equipment and voice-frequency data communication terminal equipment (June 1968).

EIA-363. Standard for specifying signal quality for transmitting and receiving data processing terminal equipment using serial data transmission at the interface with non-synchronous data communication equipment (May 1969).

EU-366-A. Interface between data terminal equipment and automatic calling equipment for data communication (March 1979).

**EIA-404–A.** Standard for start/stop signal quality between data terminal equipment and non-synchronous data communication equipment ANSI approved (January 1986).

**EIA-404-1.** Addendum No. 1 to EIA-404 and EIA-334-A. Application of signal requirements to EIA449.

**EIA-410.** Standard for electrical characteristics of class A closure interchange circuits (April 1974).

**EIA-422-A.** Electrical characteristics of balanced voltage digital interface circuits (December 1978).

**EIA-423-A.** Electrical characteristics of unbalanced voltage digital interface circuits (December 1978).

EIA-449-1. General-purpose 37-position interface for Data Terminal Equipment and Data Circuit terminating Equipment employing serial-binary data interchange. (The electrical signal characteristics for EIA-449 are defined by either EIA-422 or EIA-423, since EIA-449 is only a mechanical and functional definition standard) (February 1980).

**EIA-470-A.** Telephone instruments with loop signaling. Performance and technical criteria for connecting and interfacing various elements of the public telephone network.

EIA-491. Interface between a numerical control unit and peripheral equipment employing asynchronous binary data interchange over circuits having EIA-423-A electrical characteristics (October 1982).

EIA—496. Interface between data communication equipment (DCE) and the public switched telephone network (PSTN). ANSI approved (May 1984).

**EIA-S30.** High-speed 25-position interface for Data Terminal Equipment and Data Circuit Terminating Equipment. ANSI approved (March 1987).

V. CCITT. Code designation.

**V.1.** Equivalence between binary notation symbols and the significant conditions of a two-condition code.

V.2. Power levels for data transmission over telephone lines.

V.3. International Telegraph Alphabet No. 5.

**V.4.** General structure of signals of International Telegraph Alphabet No. 5 code for data transmission over public telephone network.

**V.5.** Standardization of data-signaling rates for synchronous data transmission in the general switched telephone network.

**V.6.** Standardization of data-signaling rates for synchronous data transmission on leased telephone-type circuits.

V.7. Definition of terms concerning data communication over the telephone network.

V.10(X.26). Electrical characteristics for unbalanced double-current interchange circuits for general use with integrated circuit equipment in the field of data communications (and provisional amendments, May 1977).

- V.11(X.27). Electrical characteristics for balanced double—current interchange circuits for general use with integrated circuit equipment in the field of data communications (and provisional amendments, May 1977).

- V.15. Use of acoustic coupling for data transmission.

- **V.19.** Modems for parallel data transmission using telephone signaling frequencies.

- **V.20.** Parallel data transmission modems standardized for universal use in the general switched telephone network.

- **V.21.** 300-bit/s full-duplex modern standardized for use in the general switched telephone network.

- **V.22.** 1200 BPS full–duplex modem standardized for use in the general switched telephone network and on point–to–point two–wire leased telephone–type circuits.

- V.22bis. 2400 BPS full-duplex modem using the frequency division technique standardized for use on the general switched telephone network and on point-to-point two-wire leased telephone-type circuits.

- **V.23.** 600/1.2K BPS modem standardized for use in the general switched telephone network.

- **V.24.** List of definitions for interchange circuits between data terminal equipment and data circuit terminating equipment (and provisional amendments, May 1977).

- V.25. Automatic calling and/or answering equipment on the general switched telephone network, including disabling of echo suppressors on manually established calls.

- V.25bis. Automatic calling and/or answering equipment on the general switched telephone network using the 100 series interchange circuits.

- **V.26.** 2.4/1.2 KBPS modem standardized for use on four–wire leased telephone–type circuits.

- **V.26bis.** 2.4/1.2 KBPS modem standardized for use in the general switched telephone network.

- V.26ter. 2.4 KBPS full-duplex modem using the echo cancellation technique standardized for use on the general switched telephone network and on point-to-point two-wire leased telephone-type circuite.

- V.27. 4.8 KBPS modem with manual equalizer standardized for use on leased telephone–type circuits.

- **V.27bis.** 4.8 KBPS modem with automatic equalizer standardized for use on leased telephone–type circuits.

- **V.27ter.** 4.8/2.4 KBPS modem standardized for use in the general switched telephone network.

- **V.28.** Electrical characteristics for unbalanced double–current interchange circuits.

- **V.29.** 9.6 KBPS modem standardized for use on point–to–point four–wire leased telephone–type circuits.

- V.31. Electrical characteristics for single—current interchange circuits controlled by contact closure.

- V.32. A family of two—wire, full—duplex modems operating at data signaling rates of up to 9600 BPS for use on the general switched telephone network and on leased telephone—type circuits.

- V.35. Data transmission at 48 KBPS using 60– to 108–kHz group band circuits. V.36. Modems for synchronous data transmission using 60– to 108–kHz group band circuits.

- V.37. Synchronous data transmission at a data signaling rate higher than 72 KBPS using 60–108 kHz group band circuits.

- V.40. Error indication with electromechanical equipment.

- V.41. Code independent error control system.

- V.50. Standard limits for transmission quality of data transmission.

- **V.51.** Organization of the maintenance of international telephone—type circuits used for data transmission.

- **V.52.** Characteristics of distortion and error–rate measuring apparatus for data transmission.

- V.53. Limits for the maintenance of telephone—type circuits used for data transmission.

- V.54. Loop test devices for modems.

- **V.55.** Specification for an impulsive noise measuring instrument for telephone–type circuits.

- V.56. Comparative tests of modems for use over telephone—type circuits.

- V.57. Comprehensive data test set for high data signaling rates.

- **V.100.** Interconnection between public data networks (PDNs) and the public switched telephone network (PSTN).

- V.110. Support of data terminal equipment (DTEs) with V-series type interfaces by an integrated services digital network (ISDN).

#### X

- X. CCITT Recommendation designation.

- X.1. International user classes of service in public data networks.

- X.2. International user facilities in public data networks.

- ${\bf X.3.}$  Packet assembly/disassembly facility (PAD) in a public data network.

- **X.4.** General structure of signals of international alphabet no. 5 code for data transmission over public data networks.

- X.20. Interface between data terminal equipment and data circuit—terminating equipment for start/stop transmission services on public data networks.

- X.20bis(V.21). Compatible interface between data terminal equipment and data circuit—terminating equipment for start/stop transmission services on public data networks.

- X.21. General-purpose interface between data terminal equipment and data circuit-terminating equipment for synchronous operation on public data networks.

- **X.21bis.** Use on public data networks of data terminal equipment that is designed for interfacing to synchronous V-series modems.

- X.24. List of definitions of interchange circuits between data terminal equipment and data circuit-terminating equipment on public data networks.

- X.25. Interface between data terminal equipment and data circuit-terminating equipment for terminals operating in the packet mode on public data networks (and provisional amendment, April 1977).

- X.26. Electrical characteristics for unbalanced double–current interchange circuits for general use with integrated circuit equipment in the field of data communications (identical to V.10).

- X.27. Electrical characteristics for balanced double–current interchange circuits for general use with integrated circuit equipment in the field of data communications (identical to V.11).

- X.28. DTE/DCE interface for start/stop mode data terminal equipment accessing the packet assembly/disassembly facility (PAD) on a public network situated in the same country.

- X.29. Procedures for exchange of control information and user data between a packet-mode DTE and a packet assembly/disassembly facility (PAD).

- **X.30.** Standardization of basic model page—printing machine in accordance with International Telegraph Alphabet No. 5.

- X.31. Characteristics, from the transmission point of view, at the interchange point between data terminal equipment and data circuit-terminating equipment in a 200 BPS start/stop data terminal.

- **X.32.** Answer–back units for 200 BPS start/stop machines in accordance with International Telegraph Alphabet No. 5.

- X.33. Standardization of an international text for the measurement of the margin of start/stop machines in accordance with International Telegraph Alphabet No. 5.

- X.92. Hypothetical reference connections for public synchronous data net- works.

- X.95. Network parameters in public data networks.

- X.96. Call progress signals in public data networks.

- X.500. A specification defining the universal interconnectivity of public electronic mail networks. X.500 implies a global directory for

- all of the different services, not just electronic mail; services include telephone, Telex, and other networks. X.500 is in its early stages of development.

- X3.1. Synchronous signaling rates for data transmission.

- X3.4. Code of information interchange.

- **X3.15.** Bit sequencing of the American National Standard Code for Information Interchange in serial—by—bit transmission.

- X3.16. Character structure and character parity sense for serial—by—bit data communication in the American National Standard Code for Information Interchange.

- **X3.24.** Signal quality at interface between data processing technical equipment for synchronous data transmission.

- **X3.25.** Character structure and character parity sense for parallel—by—bit communication in the American National Standard Code for Information Interchange.

- X3.2. Procedures for the use of communication control characters of American National Standard Code for Information Interchange in specified data communications links.

- **X3.36.** Synchronous high–speed data signaling rates between data terminal equipment and data communication equipment.

- X3.41. Code extension techniques for use with seven—bit coded character set of American National Standard Code for Information Interchange.

- X3.44. Determination of the performance of data communication systems.

- X3.57. Message heading formats for information interchange using ASCII for data communication system control.

В

# **Networking acronyms**

| 4 | ı | ١ | ۱ |  |

|---|---|---|---|--|

|   |   |   |   |  |

| AAL     | ATM Adaptation Layer, two sublayers concerned with                                                          | В          | Bearer channel, a DS-0 for user trafric.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |